# 150Mbps, Six-Channel Digital Isolator with 4 Forward Channels and 2 Reverse Channels

#### **DESCRIPTION**

The MP27942 is a six-channel digital isolator that replaces a traditional optocoupler isolator in applications. It can support up to 150Mbps of data rate signal isolation.

The MP27942 employs capacitive isolation technology to provide up to  $5kV_{RMS}$  of insulation voltage. The device offers a compact solution, with low power consumption and improved reliability compared to traditional optocoupler isolators.

A Schmitt trigger input and isolated encoding/decoding are provided for high immunity in noisy environments. The selectable high/low failsafe output supports a fixed output, even if the input signal power fails.

The MP27942 is available in an SOIC-16 wide-body (WB) package.

rovided

#### **FEATURES**

- Channel Direction: 4 Forward, 2 Reverse

- 5kV<sub>RMS</sub> Isolation Voltage

- Supports 0Mbps (DC) to 150Mbps Data Rate

- 2.5V to 5.5V Operating Range

- >±100kV/µs Common-Mode Transient Immunity (CMTI)

- High System Level ESD, EFT, and Surge Immunity Performance

- 13ns Propagation Delay for 5V Operation

- Ultra-Low Power Supply Current

- Default Output Logic High (MP27942) and Low (MP27942-L) options

- 1.2kV Maximum Working Isolation Voltage (V<sub>IORM</sub>)

- Wide -40°C to +125°C Temperature Range

- Available in an SOIC-16 Wide-Body (WB)

Package

- UL 1577 Fifth Edition Certified:

- SOIC-16 WB: 5000V<sub>RMS</sub> Isolation for 1 Minute

- CSA Component Notice 5A Approval:

- SOIC-16 WB: 5000V<sub>RMS</sub> Isolation for 1 Minute

- DIN EN IEC 60747-17 (VDE 0884-17): 2021-10 Certified:

- SOIC-16 WB: 7071V<sub>PK</sub> Isolation

- CQC Certification per GB 4943.1-2022

- CB Certification per IEC62368-1 Third Edition

#### **APPLICATIONS**

- Power Meters

- Programmable Logic Controllers (PLCs)

- Server Power

- Motor Controllers and Drivers

- Switches

- Solar Inverters

- Medical Equipment

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

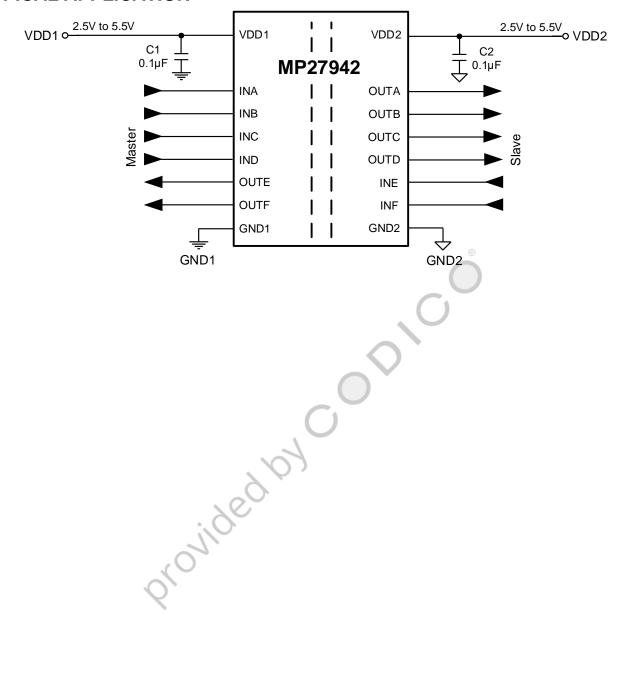

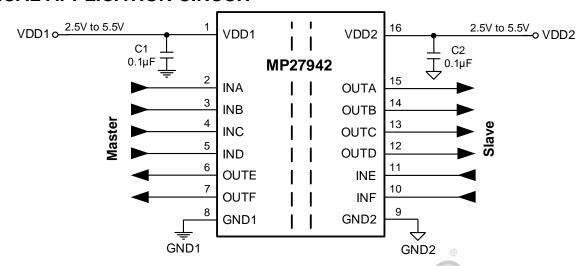

### **TYPICAL APPLICATION**

#### ORDERING INFORMATION

| Part Number* | Output Default | Package              | Top Marking | MSL Rating |

|--------------|----------------|----------------------|-------------|------------|

| MP27942GY    | High           | COIC 16 MP           | Coo Polow   | 2          |

| MP27942-LGY  | Low            | SOIC-16 WB See Belou |             | ა          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP27942GY-Z).

## **TOP MARKING (MP27942GY)**

(SOIC-16 WB, Default High)

**MPSYYWW** MP27942 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code

MP27942: Part number LLLLLLL: Lot number

## **TOP MARKING (MP27942-LGY)**

(SOIC-16 WB, Default Low)

MPS YYWW MP27942-L

LLLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code

MP27942-L: Part number LLLLLLL: Lot number

© 2023 MPS. All Rights Reserved.

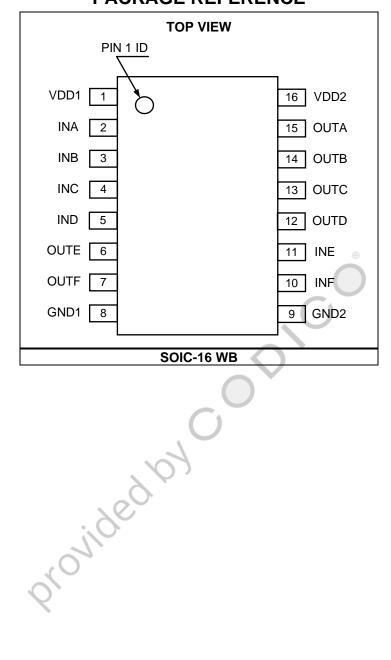

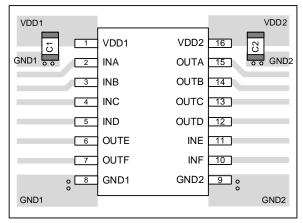

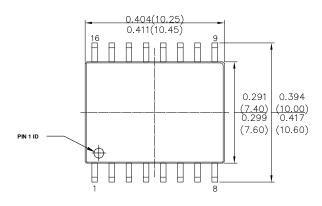

### **PACKAGE REFERENCE**

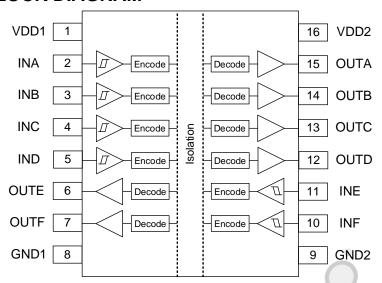

## **PIN FUNCTIONS**

| Pin # | Name | Description                                                                                                               |

|-------|------|---------------------------------------------------------------------------------------------------------------------------|

| 1     | VDD1 | <b>Side 1 power supply pin.</b> It is recommended to connect a 0.1µF decoupling capacitor between the VDD1 and GND1 pins. |

| 2     | INA  | Channel A input pin.                                                                                                      |

| 3     | INB  | Channel B input pin.                                                                                                      |

| 4     | INC  | Channel C input pin.                                                                                                      |

| 5     | IND  | Channel D input pin.                                                                                                      |

| 6     | OUTE | Channel E output pin.                                                                                                     |

| 7     | OUTF | Channel F output pin.                                                                                                     |

| 8     | GND1 | Side 1 ground pin.                                                                                                        |

| 9     | GND2 | Side 2 ground pin.                                                                                                        |

| 10    | INF  | Channel F input pin.                                                                                                      |

| 11    | INE  | Channel E input pin.                                                                                                      |

| 12    | OUTD | Channel D output pin.                                                                                                     |

| 13    | OUTC | Channel C output pin.                                                                                                     |

| 14    | OUTB | Channel B output pin.                                                                                                     |

| 15    | OUTA | Channel A output pin.                                                                                                     |

| 16    | VDD2 | <b>Side 2 power supply pin.</b> It is recommended to connect a 0.1µF decoupling capacitor between the VDD2 and GND2 pins. |

Providediby

5

## **ABSOLUTE MAXIMUM RATINGS (1)** VDD1 to GND1, VDD2 to GND2..... .....-0.3V to +6.5V Side 1 other pins to GND1..... .....-0.3V to VDD1 + 0.3V (2) Side 2 other pins to GND2..... .....-0.3V to VDD2 + 0.3V (2) Average output current per pin ..... .....-10mA to +10mA Common-mode transient immunity..... .....-100kV/µs to +100kV/µs Continuous power dissipation ( $T_A = 25^{\circ}C$ ) (3) (5) SOIC-16 WB ...... 2.2W Junction temperature (T<sub>J</sub>) ......150°C Lead temperature ......260°C Storage temperature.....-65°C to +150°C ESD Ratings Human body model (HBM).....±6000V Charged-device model (CDM).....±2000V Isolation barrier withstand with HBM......±8000V Recommended Operating Conditions (4) Supply voltage $(V_{DD1}, V_{DD2})$ .....2.5V to 5.5V Maximum signal data rate..... ......0Mbps (DC) to 150Mbps Operating junction temp (T<sub>J</sub>).... -40°C to +125°C 3KONIGEGI PÓ

| Thermal Resistance      | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |

|-------------------------|-------------------------|--------------------------|

| SOIC-16 WB              |                         |                          |

| EV27942-Y-00A (5)       | . 56.8                  | . 21.3°C/W               |

| JESD51-7 <sup>(6)</sup> | 75                      | . 48.7°C/W               |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum voltage must not exceed 6.5V.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can produce an excessive die temperature, which may cause the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on the EV27942-Y-00A, a 2-layer PCB (51mmx51mm).

- 6) The θ<sub>JA</sub> value given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

## **ELECTRICAL CHARACTERISTICS**

$V_{DD1} = V_{DD2} = 5V$ ,  $T_J = -40$ °C to +125°C (7), typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                        | Symbol                      | Condition                                                    | Min                    | Тур                    | Max | Units |

|--------------------------------------------------|-----------------------------|--------------------------------------------------------------|------------------------|------------------------|-----|-------|

| Switching Timing Characteristics                 |                             |                                                              |                        |                        |     |       |

| Minimum pulse width (8)                          | t <sub>MP</sub>             |                                                              |                        |                        | 5   | ns    |

| Propagation delay from low to high (11)          | tplH                        |                                                              |                        | 13                     | 21  | ns    |

| Propagation delay from high to low (11)          | t <sub>PHL</sub>            |                                                              |                        | 13                     | 21  | ns    |

| Pulse width distortion                           | PWD                         | t <sub>PLH</sub> - t <sub>PHL</sub>                          |                        | 1.5                    | 5.5 | ns    |

| Propagation delay skew (9)                       | t <sub>PSK(P-P)</sub>       |                                                              |                        |                        | 4.5 | ns    |

| Channel-to-channel skew                          | t <sub>PS</sub>             | For both same and opposing directions                        |                        | 1                      | 5   | ns    |

| Output rising time (11)                          | <b>t</b> R                  | C <sub>L</sub> = 15pF                                        |                        | 2.5                    |     | ns    |

| Output falling time (11)                         | t⊧                          | C <sub>L</sub> = 15pF                                        | <b>(a)</b>             | 2.5                    |     | ns    |

| Peak eye diagram jitter (10)                     | t <sub>JIT_PK</sub>         |                                                              |                        | 1.5                    |     | ns    |

| Input power failure to valid default output (11) | t <sub>SD</sub>             |                                                              |                        | 500                    |     | ns    |

| Start-up time (11)                               | tstart                      | From V <sub>DD1</sub> or V <sub>DD2</sub> on to valid output |                        | 80                     | 105 | μs    |

| Common-mode transient immunity                   | CMTI                        | $IN = 0V \text{ or } V_{DD}, V_{CM} = 1.5kV$                 | ±100                   |                        |     | kV/μs |

| Power Supply Range                               |                             |                                                              |                        |                        |     |       |

| Supply voltage range                             | $V_{DD1}$                   |                                                              | 2.5                    |                        | 5.5 | V     |

| Supply voltage range                             | $V_{DD2}$                   |                                                              | 2.5                    |                        | 5.5 | V     |

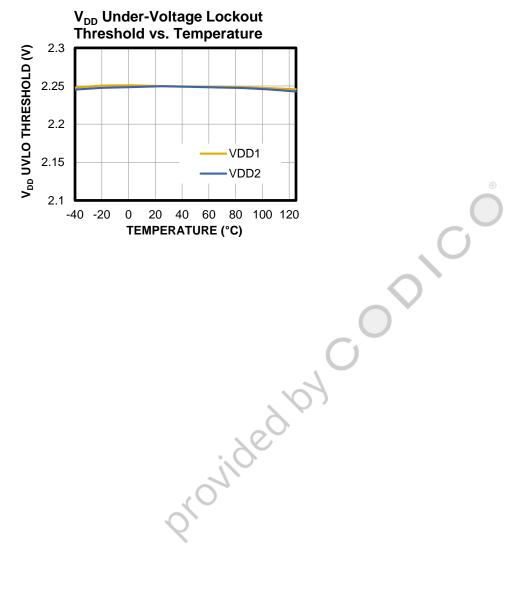

| Under-voltage lockout (UVLO)                     | $V_{\text{UVLO1\_R}}$       | V <sub>DD1</sub> rising                                      | 2.05                   | 2.25                   | 2.4 | V     |

| threshold                                        | $V_{\text{UVLO2\_R}}$       | V <sub>DD2</sub> rising                                      | 2.05                   | 2.25                   | 2.4 | V     |

| UVLO threshold hysteresis                        | V <sub>UVLO</sub> _<br>HYS1 | V <sub>DD1</sub>                                             |                        | 125                    |     | mV    |

| OVEO tillesticia hysteresis                      | Vuvlo_<br>HY\$2             | V <sub>DD2</sub>                                             |                        | 125                    |     | mV    |

| Pin Input/Output Logic Threshold                 |                             |                                                              |                        |                        |     |       |

| Input high voltage                               | V <sub>IH</sub>             | INx pins                                                     | 2                      |                        |     | V     |

| Input low voltage                                | VIL                         | IIVX PIIIS                                                   |                        |                        | 8.0 | V     |

| Pin input current leakage                        | IL                          | Connect INx to VDDx or GNDx                                  |                        |                        | ±15 | μΑ    |

| Output high voltage                              | V <sub>О</sub> Т_Н          | OUTx pins, I <sub>OUT</sub> = -4mA                           | V <sub>DDx</sub> - 0.4 | V <sub>DDx</sub> - 0.2 |     | V     |

| Output low voltage                               | V <sub>OUT_L</sub>          | OUTx pins, I <sub>OUT</sub> = 4mA                            |                        | 0.2                    | 0.4 | V     |

| Output impedance (12)                            | Z <sub>OUT</sub>            | OUTx pins                                                    |                        | 50                     |     | Ω     |

| Thermal Protection                               |                             |                                                              |                        |                        |     |       |

| Thermal shutdown temperature (10)                | T <sub>SD</sub>             |                                                              |                        | 150                    |     | °C    |

| Thermal shutdown hysteresis (10)                 | T <sub>HYS</sub>            |                                                              |                        | 20                     |     | °C    |

$V_{DD1} = V_{DD2} = 5V$ ,  $T_J = -40$ °C to +125°C (7), typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Part Number     | Parameter                                                 | Condition                                  | Min      | Тур      | Max   | Units |  |  |  |

|-----------------|-----------------------------------------------------------|--------------------------------------------|----------|----------|-------|-------|--|--|--|

| Power Supply Cu | Power Supply Current                                      |                                            |          |          |       |       |  |  |  |

| DC Supply Curre | DC Supply Current (INA/B/C/D/E/F= 0V or V <sub>DD</sub> ) |                                            |          |          |       |       |  |  |  |

|                 | VDD1 current                                              | $INx = V_{DD}$                             |          | 5        | 7.5   | mΑ    |  |  |  |

|                 | VDD1 current                                              | INx = 0V                                   |          | 12.2     | 18.3  | mΑ    |  |  |  |

| WF21942         | VDD2 current                                              | $INx = V_{DD}$                             |          | 7        | 10.5  | mΑ    |  |  |  |

|                 | VDD2 current                                              | INx = 0V                                   |          | 10.6     | 15.9  | mΑ    |  |  |  |

| MP27942-L       | VDD1 current                                              | $INx = V_{DD}$                             |          | 12.2     | 18.3  | mΑ    |  |  |  |

|                 |                                                           | INx = 0V                                   |          | 5        | 7.5   | mΑ    |  |  |  |

|                 | VDD2 current                                              | $INx = V_{DD}$                             |          | 10.6     | 15.9  | mΑ    |  |  |  |

|                 |                                                           | INx = 0V                                   |          | 7        | 10.5  | mΑ    |  |  |  |

| 1Mbps Supply Cu | irrent (INA/B/C/D/E/F = \$                                | 500kHz Square Wave, C <sub>LOAD</sub> = 15 | pF on A  | II Outpu | ıts)  |       |  |  |  |

| MP27942,        | VDD1 current                                              |                                            | <b>(</b> | 6.6      | 13.1  | mΑ    |  |  |  |

| MP27942-L       | VDD2 current                                              |                                            |          | 7.7      | 13.5  | mΑ    |  |  |  |

| 10Mbps Supply C | Current (INA/B/C/D/E/F =                                  | 5MHz Square Wave, CLOAD = 15               | pF on A  | II Outpu | ıts)  |       |  |  |  |

| MP27942,        | VDD1 current                                              |                                            |          | 7.7      | 14.4  | mΑ    |  |  |  |

| MP27942-L       | VDD2 current                                              |                                            |          | 10.2     | 16.2  | mΑ    |  |  |  |

| 100Mbps Supply  | Current (INA/B/C/D/E/F                                    | = 50MHz Square Wave, CLOAD = 1             | 5 pF on  | All Out  | puts) |       |  |  |  |

| MP27942,        | VDD1 current                                              |                                            |          | 19       | 27.9  | mA    |  |  |  |

| MP27942-L       | VDD2 current                                              |                                            |          | 34.9     | 47.5  | mΑ    |  |  |  |

Provided by

$V_{DD1} = V_{DD2} = 3.3V$ ,  $T_J = -40$ °C to +125°C (7), typical values are tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                        | Symbol                      | Condition                                                    | Min                    | Тур                    | Max | Units |

|--------------------------------------------------|-----------------------------|--------------------------------------------------------------|------------------------|------------------------|-----|-------|

| Switching Timing Characteristics                 |                             |                                                              |                        |                        |     |       |

| Minimum pulse width (8)                          |                             |                                                              |                        |                        | 5   | ns    |

| Propagation delay from low to high (11)          | t <sub>PLH</sub>            |                                                              |                        | 14                     | 22  | ns    |

| Propagation delay from high to low (11)          | t <sub>PHL</sub>            |                                                              |                        | 14                     | 22  | ns    |

| Pulse width distortion                           | PWD                         | tplh - tphl                                                  |                        | 1.5                    | 5.5 | ns    |

| Propagation delay skew (9)                       | tpsk(p-p)                   |                                                              |                        |                        | 4.5 | ns    |

| Channel-to-channel skew                          | t <sub>PS</sub>             | For both same and opposing directions                        |                        | 1                      | 5   | ns    |

| Output rising time (11)                          | t <sub>R</sub>              | C <sub>L</sub> = 15pF                                        |                        | 3.5                    |     | ns    |

| Output falling time (11)                         | t⊧                          | C <sub>L</sub> = 15pF                                        | <b>®</b>               | 3.5                    |     | ns    |

| Peak eye diagram jitter (10)                     | t <sub>JIT_PK</sub>         |                                                              |                        | 1.5                    |     | ns    |

| Input power failure to valid default output (11) | tsp                         |                                                              |                        | 500                    |     | ns    |

| Start-up time (11)                               | <b>t</b> start              | From V <sub>DD1</sub> or V <sub>DD2</sub> on to valid output |                        | 80                     | 105 | μs    |

| Common-mode transient immunity                   | CMTI                        | $IN = 0V$ or $V_{DD}$ , $V_{CM} = 1.5kV$                     | ±100                   |                        |     | kV/μs |

| Power Supply Range                               | •                           |                                                              |                        |                        |     |       |

| Complements and an arrange                       | V <sub>DD1</sub>            |                                                              | 2.5                    |                        | 5.5 | V     |

| Supply voltage range                             | V <sub>DD2</sub>            | ()                                                           | 2.5                    |                        | 5.5 | V     |

| LIV/LO throubold                                 | V <sub>UVLO1_R</sub>        | V <sub>DD1</sub> rising                                      | 2.05                   | 2.25                   | 2.4 | V     |

| UVLO threshold                                   | V <sub>UVLO2_R</sub>        | V <sub>DD2</sub> rising                                      | 2.05                   | 2.25                   | 2.4 | V     |

| LIVI O threehold by storesis                     | V <sub>UVLO</sub> _<br>HYS1 | V <sub>DD1</sub>                                             |                        | 125                    |     | mV    |

| UVLO threshold hysteresis                        | Vuvlo_<br>HYS2              | V <sub>DD2</sub>                                             |                        | 125                    |     | mV    |

| Pin Input/Output Logic Threshold                 | •                           |                                                              |                        |                        |     |       |

| Input high voltage                               | ViH                         | INx                                                          | 2                      |                        |     | V     |

| Input low voltage                                | VIL                         |                                                              |                        |                        | 0.8 | V     |

| Pin input current leakage                        | ΙL                          | Connect INx to VDDx or GNDx                                  |                        |                        | ±15 | μA    |

| Output high voltage                              | V <sub>О</sub> Т_Н          | OUTx pins, I <sub>OUT</sub> = -4mA                           | V <sub>DDx</sub> - 0.4 | V <sub>DDx</sub> - 0.2 |     | V     |

| Output low voltage                               | V <sub>OUT_L</sub>          | OUTx pins, Iout = 4mA                                        |                        | 0.2                    | 0.4 | V     |

| Output impedance (12)                            | Zout                        | OUTx pins                                                    |                        | 50                     |     | Ω     |

| Thermal Protection                               |                             |                                                              |                        |                        |     |       |

| Thermal shutdown temperature (10)                | T <sub>SD</sub>             |                                                              |                        | 150                    |     | °C    |

| Thermal shutdown hysteresis (10)                 | T <sub>HYS</sub>            |                                                              |                        | 20                     |     | °C    |

© 2023 MPS. All Rights Reserved.

$V_{DD1}$  =  $V_{DD2}$  = 3.3V,  $T_J$  = -40°C to +125°C  $^{(7)}$ , typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Part Number             | Parameter                 | Condition                      | Min      | Тур      | Max   | Units |

|-------------------------|---------------------------|--------------------------------|----------|----------|-------|-------|

| <b>Power Supply Cu</b>  |                           |                                |          |          |       |       |

| <b>DC Supply Currer</b> | nt (INA/B/C/D/E/F= 0V o   | r V <sub>DD</sub> )            |          |          |       |       |

|                         | VDD1 current              | $INx = V_{DD}$                 |          | 5        | 7.5   | mΑ    |

| MP27942                 | VDD1 current              | INx = 0V                       |          | 12.2     | 18.3  | mΑ    |

| IVIF 21 942             | VDD2 current              | $INx = V_{DD}$                 |          | 7        | 10.5  | mΑ    |

| MP27942-L               | VDD2 current              | INx = 0V                       |          | 10.6     | 15.9  | mΑ    |

|                         | VDD1 current              | $INx = V_{DD}$                 |          | 12.2     | 18.3  | mΑ    |

| MD27042 I               | VDD1 current              | INx = 0V                       |          | 5        | 7.5   | mΑ    |

|                         | VDD2 current              | $INx = V_{DD}$                 |          | 10.6     | 15.9  | mΑ    |

|                         | VDD2 current              | INx = 0V                       |          | 7        | 10.5  | mΑ    |

| 1Mbps Supply Cu         | rrent (INA/B/C/D/E/F = \$ | 500kHz Square Wave, CLOAD = 15 | oF on A  | II Outpu | ts)   |       |

| MP27942,                | VDD1 current              |                                | <b>®</b> | 6.5      | 13    | mA    |

| MP27942-L               | VDD2 current              |                                |          | 7.5      | 13.4  | mΑ    |

| 10Mbps Supply C         | urrent (INA/B/C/D/E/F =   | 5MHz Square Wave, CLOAD = 15p  | F on Al  | l Output | s)    |       |

| MP27942,                | VDD1 current              |                                |          | 7.2      | 14.1  | mΑ    |

| MP27942-L               | VDD2 current              |                                |          | 9.1      | 15.7  | mΑ    |

| 100Mbps Supply          | Current (INA/B/C/D/E/F    | = 50MHz Square Wave, CLOAD = 1 | 5pF on   | All Outp | outs) |       |

| MP27942,                | VDD1 current              |                                |          | 15.1     | 25.2  | mΑ    |

| MP27942-L               | VDD2 current              |                                |          | 25.5     | 37.8  | mΑ    |

|                         | Provide                   | ed by                          |          |          |       |       |

$V_{DD1}$  =  $V_{DD2}$  = 2.5V,  $T_J$  = -40°C to +125°C  $^{(7)}$ , typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                        | Symbol                      | Condition                                                    | Min                    | Тур                    | Max | Units |

|--------------------------------------------------|-----------------------------|--------------------------------------------------------------|------------------------|------------------------|-----|-------|

| Switching Timing Characteristics                 |                             |                                                              |                        |                        |     |       |

| Minimum pulse width (8)                          | t <sub>MP</sub>             |                                                              |                        |                        | 5   | ns    |

| Propagation delay from low to high (11)          | tplH                        |                                                              |                        | 15                     | 23  | ns    |

| Propagation delay from high to low (11)          | tphL                        |                                                              |                        | 15                     | 23  | ns    |

| Pulse width distortion                           | PWD                         | tplh - tphl                                                  |                        | 1.5                    | 5.5 | ns    |

| Propagation delay skew (9)                       | tPSK(P-P)                   |                                                              |                        |                        | 4.5 | ns    |

| Channel-to-channel skew                          | t <sub>PS</sub>             | For both same and opposing directions                        |                        | 1                      | 5   | ns    |

| Output rising time (11)                          | t <sub>R</sub>              | C <sub>L</sub> = 15pF                                        |                        | 4.5                    |     | ns    |

| Output falling time (11)                         | t⊧                          | C <sub>L</sub> = 15pF                                        | <b>®</b>               | 4.5                    |     | ns    |

| Peak eye diagram jitter (10)                     | t <sub>JIT_PK</sub>         |                                                              |                        | 1.5                    |     | ns    |

| Input power failure to valid default output (11) | t <sub>SD</sub>             |                                                              |                        | 500                    |     | ns    |

| Start-up time (11)                               | <b>t</b> start              | From V <sub>DD1</sub> or V <sub>DD2</sub> on to valid output |                        | 80                     | 105 | μs    |

| Common-mode transient immunity                   | CMTI                        | $IN = 0V \text{ or } V_{DD}, V_{CM} = 1.5kV$                 | ±100                   |                        |     | kV/μs |

| Power Supply Range                               |                             |                                                              |                        |                        |     |       |

| Supply voltage range                             | $V_{DD1}$                   |                                                              | 2.5                    |                        | 5.5 | V     |

| Supply voltage range                             | $V_{DD2}$                   |                                                              | 2.5                    |                        | 5.5 | V     |

| UVLO threshold                                   | $V_{\text{UVLO1\_R}}$       | V <sub>DD1</sub> rising                                      | 2.05                   | 2.25                   | 2.4 | V     |

| OVEO tillesiloid                                 | $V_{\text{UVLO2\_R}}$       | V <sub>DD2</sub> rising                                      | 2.05                   | 2.25                   | 2.4 | V     |

| UVLO threshold hysteresis                        | V <sub>UVLO</sub> _<br>HYS1 | V <sub>DD1</sub>                                             |                        | 125                    |     | mV    |

| UVLO tillesiloid flysteresis                     | Vuvlo_<br>HYS2              | V <sub>DD2</sub>                                             |                        | 125                    |     | mV    |

| Pin Input/Output Logic Threshold                 |                             |                                                              |                        |                        |     |       |

| Input high voltage                               | ViH                         | INx                                                          | 2                      |                        |     | V     |

| Input low voltage                                | VIL                         | II VA                                                        |                        |                        | 8.0 | V     |

| Pin input current leakage                        | lι                          | Connect INx to VDDx or GNDx                                  |                        |                        | ±15 | μΑ    |

| Output high voltage                              | V <sub>OUT_H</sub>          | OUTx pins, I <sub>OUT</sub> = -4mA                           | V <sub>DDx</sub> - 0.4 | V <sub>DDx</sub> - 0.2 |     | V     |

| Output low voltage                               | V <sub>OUT_L</sub>          | OUTx pins, I <sub>OUT</sub> = 4mA                            |                        | 0.2                    | 0.4 | V     |

| Output impedance (12)                            | Zout                        | OUTx pins                                                    |                        | 50                     |     | Ω     |

| Thermal Protection                               |                             |                                                              |                        |                        |     |       |

| Thermal shutdown temperature (10)                | T <sub>SD</sub>             |                                                              |                        | 150                    |     | °C    |

| Thermal shutdown hysteresis (10)                 | T <sub>HYS</sub>            |                                                              |                        | 20                     |     | °C    |

$V_{DD1} = V_{DD2} = 2.5V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  (7), typical values are tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Part Number     | Parameter                                                 | Condition                       | Min      | Тур      | Max   | Units |  |  |

|-----------------|-----------------------------------------------------------|---------------------------------|----------|----------|-------|-------|--|--|

| Power Supply C  | Power Supply Current                                      |                                 |          |          |       |       |  |  |

| DC Supply Curre | DC Supply Current (INA/B/C/D/E/F= 0V or V <sub>DD</sub> ) |                                 |          |          |       |       |  |  |

| MP27942         | VDD1 current                                              | $INx = V_{DD}$                  |          | 5        | 7.5   | mΑ    |  |  |

|                 | VDD1 current                                              | INx = 0V                        |          | 12.2     | 18.3  | mΑ    |  |  |

|                 | VDD2 current                                              | $INx = V_{DD}$                  |          | 7        | 10.5  | mΑ    |  |  |

|                 | VDD2 current                                              | INx = 0V                        |          | 10.6     | 15.9  | mΑ    |  |  |

| MP27942-L       | VDD1 current                                              | $INx = V_{DD}$                  |          | 12.2     | 18.3  | mΑ    |  |  |

|                 |                                                           | INx = 0V                        |          | 5        | 7.5   | mΑ    |  |  |

|                 | VDD2 current                                              | $INx = V_{DD}$                  |          | 10.6     | 15.9  | mΑ    |  |  |

|                 |                                                           | INx = 0V                        |          | 7        | 10.5  | mΑ    |  |  |

| 1Mbps Supply C  | urrent (INA/B/C/D/E/F =                                   | 500kHz Square Wave, CLOAD = 15  | pF on A  | II Outpu | ıts)  |       |  |  |

| MP27942,        | VDD1 current                                              |                                 | <b>®</b> | 6.4      | 13    | mΑ    |  |  |

| MP27942-L       | VDD2 current                                              |                                 |          | 7.4      | 13.4  | mΑ    |  |  |

| 10Mbps Supply   | Current (INA/B/C/D/E/F :                                  | = 5MHz Square Wave, CLOAD = 15p | F on Al  | I Outpu  | ts)   |       |  |  |

| MP27942,        | VDD1 current                                              |                                 | 4        | 7.0      | 13.8  | mΑ    |  |  |

| MP27942-L       | VDD2 current                                              |                                 |          | 8.6      | 15    | mΑ    |  |  |

| 100Mbps Supply  | Current (INA/B/C/D/E/F                                    | = 50MHz Square Wave, CLOAD = 1  | 5pF on   | All Out  | outs) |       |  |  |

| MP27942,        | VDD1 current                                              |                                 |          | 13.4     | 21.9  | mΑ    |  |  |

| MP27942-L       | VDD2 current                                              |                                 |          | 19.3     | 31.2  | mΑ    |  |  |

#### Notes:

- 7) Not tested in production. Derived by over-temperature correlation.

- 8) Derived by go/no-go test.

- 9) t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltage, load, and ambient temperature.

- 10) Derived by sample characterization. Not tested in production.

- 11) See Figure 4 and Figure 5 on page 20, and Figure 6 on page 21 for more details.

- 12) The nominal output impedance of an isolator driver channel is approximately 50Ω ±40%, which is a sum of the value of the on-chip series termination resistor and the output driver FET's channel resistance. When driving loads where transmission line effects may be a factor, ensure that the output pins are appropriately terminated with controlled-impedance PCB traces.

## **REGULATORY INFORMATION**

| UL                                                                                | CSA                                                                               | VDE (IEC)                                                                                                                                                                                       | CQC                                                                                                                                                                         |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Certified according to UL1577 Component Recognition Program                       | Certified according to<br>CSA Component<br>Acceptance Service<br>Notice No.5A     | Certified according to DIN<br>EN IEC 60747-17<br>(VDE 0884-17): 2021-10;<br>EN IEC 60747-17: 2020 +<br>AC: 2021                                                                                 | Certified according to GB 4943.1-2022                                                                                                                                       |

| SOIC-16 WB package:<br>single protection,<br>5000V <sub>RMS</sub> <sup>(13)</sup> | SOIC-16 WB package:<br>single protection,<br>5000V <sub>RMS</sub> <sup>(13)</sup> | Basic isolation:  Maximum transient isolation voltage: 7071V <sub>PK</sub> Maximum repetitive peak isolation voltage: 1200 V <sub>PK</sub> Maximum surge isolation voltage: 3077V <sub>PK</sub> | Altitude ≤ 5000m, tropical climate:  • Reinforced insulation: 600V <sub>RMS</sub> maximum working voltage  • Basic insulation: 1000V <sub>RMS</sub> maximum working voltage |

| File (E322138)                                                                    | File (E322138)                                                                    | File (40055422)                                                                                                                                                                                 | File (CQC22001348724)                                                                                                                                                       |

#### Note:

### **INSULATION SPECIFICATIONS**

| Parameter                                        | Symbol | Condition                                                                                                                             | SOIC-16 WB | Units     |

|--------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| External clearance (14)                          | CLR    | According to IEC 60664-1 (VDE 0110-1): shortest pinto-pin distance through the air between the primary and secondary sides            | >8         | mm        |

| External creepage (14)                           | CPG    | According to IEC 60664-1 (VDE 0110-1): shortest pinto-pin distance across the package surface between the primary and secondary sides | >8         | mm        |

| Minimum internal gap                             | DTI    | Internal clearance                                                                                                                    | >20        | μm        |

| Tracking resistance (comparative tracking index) | СТІ    | According to IEC 60112                                                                                                                | >600       | $V_{RMS}$ |

| Material group                                   | 5      | According to IEC 60664-1                                                                                                              | I          | -         |

| Over-voltage category                            | X      | Rated mains voltages ≤ 150V <sub>RMS</sub>                                                                                            | I-IV       | -         |

| per IEC 60664-1                                  | -      | Rated mains voltages ≤ 300V <sub>RMS</sub>                                                                                            | I-IV       | -         |

| per 120 00004-1                                  |        | Rated mains voltages ≤ 600V <sub>RMS</sub>                                                                                            | 1-111      | -         |

#### Note:

<sup>13)</sup> The regulatory certification applies to  $5000V_{\text{RMS}}$  rated devices that are production tested to  $6000V_{\text{RMS}}$  for 1s.

<sup>14)</sup> See the Package Information section on page 24 for more detailed dimensions. For isolated solutions, the recommended land pattern is used to maintain sufficient safety creepage and clearance distances on the PCB.

#### INSULATION CHARACTERISTICS

| Parameter                         | Symbol            | Condition                                                                                                                                                                                           | SOIC-16 WB        | Units |

|-----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|

| UL 1577, Fifth Edition            |                   |                                                                                                                                                                                                     |                   |       |

| Isolation voltage rating          | V <sub>ISO</sub>  | Refer to V <sub>RMS</sub> Qualification test: V <sub>TEST</sub> = V <sub>ISO</sub> , t = 60s  100% production test: V <sub>TEST</sub> = V <sub>ISO</sub> x 1.2, t = 1s  (100% Production Test)      | 5000              | V     |

| <b>DIN EN IEC 60747-17 (VI</b>    | DE 0884-17        | '): 2021-10 <sup>(17)</sup>                                                                                                                                                                         |                   |       |

| Maximum working isolation voltage | V <sub>IORM</sub> | Refer to V <sub>PEAK</sub>                                                                                                                                                                          | 1200              | V     |

|                                   |                   | Method B1 (routine test): 100% production test: $V_{PD(M)} = 1.875 \times V_{IORM}$ , $t_M = 1s$                                                                                                    | <5                | рС    |

| Apparent charge (15)              | Q <sub>PD</sub>   | Qualification test:  Method A, after sample test and sub-group 1: $V_{PD(M)} = V_{IORM} \times 1.3$ , $t_M = 10s$ After type test sub-group 2/3: $V_{PD(M)} = V_{IORM} \times 1.2$ , $t_M = 10s$    | <b>&lt;</b> 5     | рС    |

| Transient over-voltage            | Vютм              | Refer to V <sub>PEAK</sub> Qualification test: V <sub>TEST</sub> = V <sub>IOTM</sub> for t = 60s (Qualification Test)  100% production test: V <sub>TEST</sub> = V <sub>IOTM</sub> x 1.2 for t = 1s | 7071              | V     |

| Maximum surge isolation voltage   | Viosm             | Refer to V <sub>PEAK</sub> Qualification test, tested with surge waveform 1.2µs/50µs, V <sub>TEST</sub> = V <sub>ISOM</sub> x 1.3                                                                   | 3077              | V     |

| Barrier capacitance (16)          | C <sub>IO</sub>   | Test frequency = 1MHz                                                                                                                                                                               | 2                 | рF    |

|                                   |                   | $V_{IO} = 500V, T_A = 25^{\circ}C$                                                                                                                                                                  | >10 <sup>12</sup> | Ω     |

| Insulation resistance (16)        | $R_{IO}$          | $V_{10} = 500V, 100^{\circ}C \leqslant T_{A} \le 125^{\circ}C$                                                                                                                                      | >10 <sup>11</sup> | Ω     |

|                                   |                   | $V_{10} = 500V$ , $T_A = T_S = 150$ °C                                                                                                                                                              | >10 <sup>9</sup>  | Ω     |

| Pollution degree                  |                   | 7 4                                                                                                                                                                                                 | 2                 |       |

| Climatic category                 |                   |                                                                                                                                                                                                     | 40/125/21         |       |

#### Notes:

- 15) Electrical discharge caused by a partial discharge in the coupler.

- 16) The primary-side terminals, as well as the secondary-side terminals of the barrier, are connected together, forming a two-terminal device. Then C<sub>IO</sub> and R<sub>IO</sub> are measured between the two terminals of the coupler.

- 17) This coupler is suitable for basic electrical insulation only within the maximum operating ratings. Compliance with the safety ratings are ensured by means of suitable protective circuits.

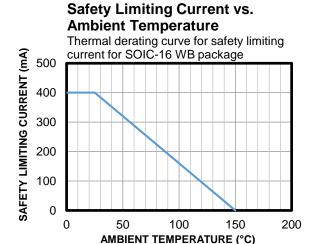

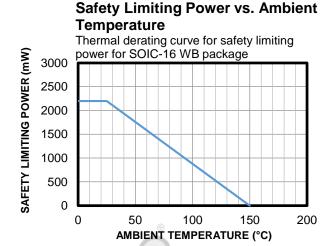

## **SAFETY LIMITING VALUES (18)**

| Parameter                                 | Symbol | Condition                                                             | SOIC-16 WB | Units |

|-------------------------------------------|--------|-----------------------------------------------------------------------|------------|-------|

| Maximum safety temperature (19)           | Ts     |                                                                       | 150        | ô     |

| Safety input, output, or supply current   | Is     | V <sub>DD</sub> = 5.5V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C | 400        | mA    |

| Safety input, output, or total power (20) | Ps     | T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                         | 2200       | mW    |

#### Notes:

- 18) These are the maximum values allowed in the event of a failure.

- 19) The maximum safety temperature (T<sub>S</sub>) has the same value as the maximum junction temperature, T<sub>J</sub> (MAX), specified in the Absolute Maximum Ratings section on page 6.

- 20) The safety power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ :  $T_S = T_J$  (MAX) =  $T_A + (\theta_{JA} \times P_S)$ .

#### THERMAL DERATING CURVE FOR SAFETY LIMITING VALUES

provided by

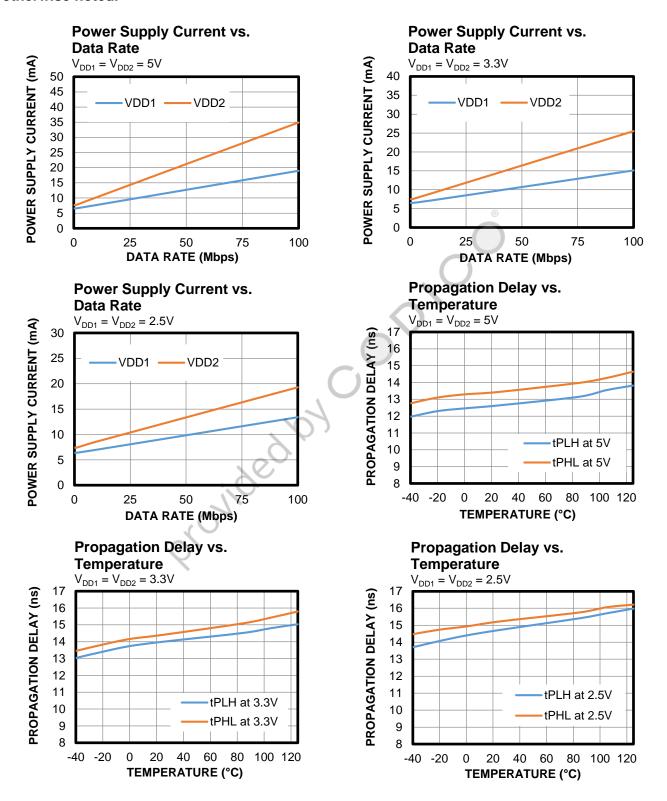

#### TYPICAL CHARACTERISTICS

$V_{DD1} = V_{DD2} = 5V$ , INA, INB, INC, IND, INE and INF = 5MHz square waveform,  $T_A = 25$ °C, unless otherwise noted.

$V_{DD1}$  =  $V_{DD2}$  = 5V, INA, INB, INC, IND, INE and INF = 5MHz square waveform,  $T_A$  = 25°C, unless otherwise noted.

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

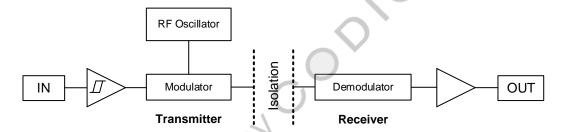

Figure 2: Isolated Signal Modulation Diagram

### **OUTPUT TRUTH TABLE**

Table 1: Truth Table (21)

| Input Side VDD Output Side VDD |                  | IN       | OUT                                    |  |  |  |

|--------------------------------|------------------|----------|----------------------------------------|--|--|--|

| Normal Working State           |                  |          |                                        |  |  |  |

| Powered                        | Powered          | High     | High                                   |  |  |  |

| Powered                        | Powered          | Low      | Low                                    |  |  |  |

| Powered                        | Powered          | Floating | High for MP27942,<br>Low for MP27942-L |  |  |  |

| VDD Off State                  |                  |          |                                        |  |  |  |

| Not powered (22)               | Powered          | х        | High for MP27942,<br>Low for MP27942-L |  |  |  |

| Х                              | Not powered (22) | Х        | I                                      |  |  |  |

#### Notes:

- 21) For this table, Hi-Z = high impedance; x = not applicable; floating = not connected; I = indeterminate; High = high-level voltage; Low = low-

- 22) An I/O can power the die for a given side through an internal diode if its source has adequate current.

19 MP27942 Rev. 1.01 MonolithicPower.com 10/3/2023

## **OPERATION**

The MP27942 is a six-channel digital isolator that replaces a traditional optocoupler isolator in applications. It adopts capacitive isolation technology, and can support up to a  $5kV_{RMS}$  insulation voltage rating and 150Mbps of data rate signal isolation.

#### **Signal Isolation Function**

The MP27942 supports a 5kV<sub>RMS</sub> voltage isolation between two sides. The data signals applied on the INx pins are transmitted to the corresponding OUTx pin through the internal isolation barrier. Figure 1 on page 18 shows the IC diagram, and Figure 2 on page 18 shows the isolated signal transmission structures.

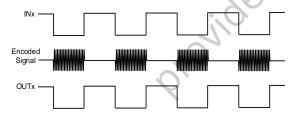

Each signal channel consists of an RF transmitter and RF receiver, separated by a semiconductor-based isolation barrier. On the input port, the transmitter modulates the signal through an RF oscillator. When the input signal is high, the RF oscillator stays off. When the input signal is low, the RF oscillator stays on. On the receiver's side, a demodulator decodes the input state according to its RF energy content, and then applies the result to the output pin. This modulation signal provides low power consumption and improved immunity for the magnetic fields. Figure 3 shows the modulation scheme.

Figure 3: Signal Modulation Scheme

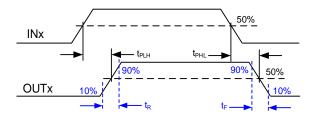

All channel signals have a Schmitt trigger input to enhance noise immunity. At the same time, all channels going in the same direction are optimized for propagation delay matching. This function can be used for serial peripheral interface (SPI) isolation, with an excellent channel-to-channel skew. Figure 4 shows the propagation delay time.

**Figure 4: Propagation Delay Time**

#### **Fail-safe Operation**

If an input power supply is not applied, then the MP27942's default output is high. If an input power supply is not applied, then the MP27942-L's default output is low.

By implementing a predetermined failsafe output, the device can ensure DC validity in the absence of input logic transitions. This means that the MP27942 can be used for SPI isolation, which prevents the slave device from being accidentally selected during a power failure status.

#### **Power Supply**

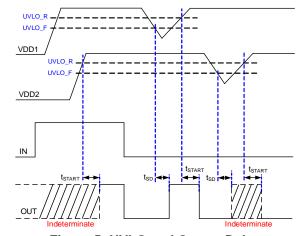

Both VDD1 and VDD2 have an under-voltage lockout (UVLO) function to prevent erroneous operation during device start-up and shutdown, or when the corresponding  $V_{DDx}$  is low.

The outputs stay at a high impedance during start-up until the corresponding  $V_{DDx}$  exceeds its UVLO threshold for the set time period ( $t_{START}$ ). After this period, the outputs follow the state of the inputs. Figure 5 shows the UVLO delay function.

Figure 5: UVLO and Output Delay

Each side can enter or exit UVLO independently, even while the output states are different. For example, if VDD1 initiates UVLO, then the side 2 output stays high as long as VDD2 is on. If VDD2 initiates UVLO, the side 2 output enters a high impedance state, even if VDD1 is on. This feature can prevent outputs from incorrectly flipping during  $V_{\text{DDx}}$  start-up.

#### **Output Short Protection**

When the OUT pin outputs an overload or short to GND, an internal current-limit circuit prevents the current from running too high. In addition, if the die temperature rises too high due to the high current, the device triggers thermal protection.

#### **Thermal Protection**

The MP27942 has an over-temperature protection (OTP) function to protect the device from excessive power dissipation during fault conditions. The thermal protection circuit disables the driver outputs when a die temperature rises to 150°C. There is a hysteresis of about 20°C, meaning that the driver outputs are re-enabled and operate normally once the junction temperature drops to about 130°C.

#### **Common-Mode Transient Immunity (CMTI)**

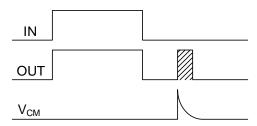

Common-mode transient immunity (CMTI) is one of the key characteristics that determine an isolator's robustness. CMTI is especially important in high-voltage applications that utilize devices with a fast transient response.

When a power device is switching, the high slew rate dV/dt or dl/dt transient noise can corrupt the signal transmission across the isolation barrier (see Figure 6).

Figure 6: Common-Mode Transient Affects

Transmission

CMTI is defined as the maximum tolerable rate of rising (or falling) for a common-mode voltage applied between two isolated circuits, most often in volts per second (V/ns or kV/µs). The isolator's output remains at the specified logic level and timing as long as the common-mode voltage remains below the maximum slew rate defined by CMTI.

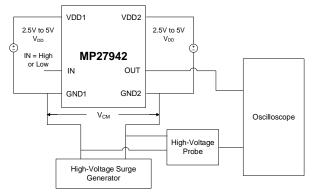

Figure 7 shows the CMTI test set-up to measure the CMTI of a coupler under the specified common-mode pulse magnitude ( $V_{\text{CM}}$ ), the specified slew rate for the common-mode pulse ( $dV_{\text{CM}}/dt$ ), and other specified test or ambient conditions. The isolator's output should remain in the correct state as long as the pulse magnitude and the slew rate meet the relevant CMTI specifications.

Figure 7: CMTI Test Circuit

#### **APPLICATION INFORMATION**

#### **Bypass Capacitor**

A  $0.1\mu F$  capacitor is recommended to ensure reliable propagation. The bypass capacitor should be placed as close to power supply and ground pins as possible.

#### **Design Example**

Table 2 is a design example following the application guidelines for the specifications below.

**Table 2: Design Example**

| V <sub>DD1</sub> | $V_{DD2}$    |  |  |

|------------------|--------------|--|--|

| 2.5V to 5.5V     | 2.5V to 5.5V |  |  |

For the detailed application schematic, see Figure 9 on page 23. For more device applications, refer to the related evaluation board datasheet(s).

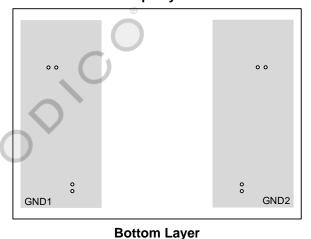

#### **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. For the best results, refer to Figure 8 and follow the guidelines below:

- 1. The primary side and secondary side must be physically separated for safety reasons.

- 2. The creepage and clearance must meet the standards for the required application.

- Minimize the loop area between signal traces and GND to avoid coupling noise in the system.

- 4. Route signal traces away from other highspeed traces or switching nodes, such as the transformer, power inductor, and MOSFET.

- 5. Place two ceramic input decoupling capacitors as close as possible to the VDD1 and GND1 pins, and VDD2 and GND2 pins.

- 6. Implement a 4-layer PCB for high-speed signals to improve EMI and signal propagation performance.

- 7. When stacking layers, stack in the following order: high-speed signal, solid GND plane, VDD plane, and low-frequency signal.

**Top Layer**

Figure 8: Recommended PCB Layout

#### TYPICAL APPLICATION CIRCUIT

Figure 9: Typical Application Circuit (6 Channels, Channel Direction: 4 Forward and 2 Reverse, Isolated Interface)

Providediby

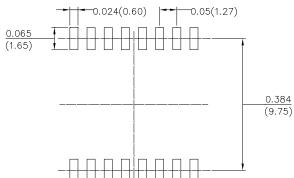

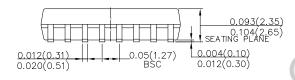

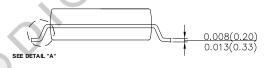

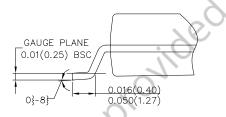

### **PACKAGE INFORMATION**

## **SOIC-16 WB (HV Isolation)**

#### **TOP VIEW**

RECOMMENDED LAND PATTERN

#### **FRONT VIEW**

**SIDE VIEW**

DETAIL "A"

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-013, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

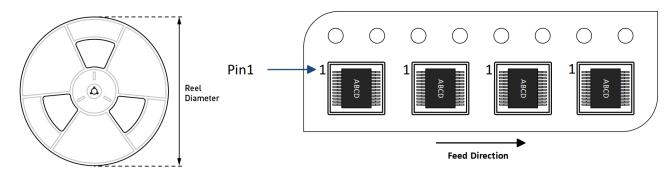

### **CARRIER INFORMATION**

| Part Number                  | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape Width | Carrier<br>Tape Pitch |

|------------------------------|------------------------|-------------------|-------------------|-------------------|------------------|-----------------------|-----------------------|

| MP27942GY-Z<br>MP27942-LGY-Z | SOIC-16<br>WB          | 1000              | N/A               | N/A               | 13in             | 24mm                  | 12mm                  |

|                              |                        |                   |                   |                   | 0                |                       |                       |

|                              |                        |                   |                   |                   |                  |                       |                       |

|                              |                        |                   | W)                |                   |                  |                       |                       |

|                              | , QX                   | jided             |                   |                   |                  |                       |                       |

|                              | ble                    | )                 |                   |                   |                  |                       |                       |

|                              |                        |                   |                   |                   |                  |                       |                       |

#### **REVISION HISTORY**

| Revision # | Revision Date | Description                    | Pages Updated |

|------------|---------------|--------------------------------|---------------|

| 1.0        | 5/17/2023     | Initial Release                | -             |

| 1.01       | 10/3/2023     | Updated Quantity/Tube to "N/A" | 25            |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.