# MP3714

3-Cell to 16-Cell, High-Accuracy Battery Monitor and Protector with Coulomb Counting

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

### DESCRIPTION

The MP3714 is a robust battery management device, providing a complete analog front-end (AFE) monitoring and protection solution. The device can support I<sup>2</sup>C or SPI communication. It supports connections for 3-cell to 16-cell series battery packs, with an absolute voltage exceeding 80V on particular pins.

The MP3714 integrates two separate analog-todigital converters (ADCs). The first ADC measures each channel's differential cell voltages (up to 16 channels), die temperature, and 7-channel temperatures via external NTC thermistors. The second ADC measures the charge/discharge current via an external currentsense resistor. The dual ADC architecture enables synchronous voltage and current measurements for cell and pack impedance monitoring.

When paired with an MPF4279x fuel gauge, the MP3714 can achieve state-of-charge (SOC) accuracy to within 2%.

The MP3714 includes high-side MOSFET (HS-FET) drivers for charge and discharge independent control. The discharge (DSG) MOSFET driver includes a configurable-scaled current soft start (SS) that provides a controlled turn-on, eliminating the need for an external precharge circuit. The MOSFET drivers also incorporate over-current protection (OCP), short-circuit protection (SCP), battery undervoltage protection (UVP), battery over-voltage protection (OVP), and high/low-temperature protection. All of these protections have configurable thresholds.

The MP3714 integrates the fuse driver for the severe under-voltage protection (SUVP), severe over-voltage protection (SOVP), MOSFET damage protection, and abundant self-diagnostics protection.

Internal passive balancing MOSFETs can be used to equalize mismatched cells, supporting up to 58mA. There is also the option to drive external balancing transistors (MOSFET or BJT).

### FEATURES

- Incorporates Dual ADC Architecture:

- <±2% State-of-Charge (SOC) Error with MPF4279x Fuel Gauge

- Cell Voltage Measurement Error <5mV

- Current/Coulomb Counter Error <±0.3%</li>

- Strictly Synchronized Current/Voltage Measurement for Impedance Sensing

- Standalone mode

- AFE can work in standalone mode without MCU

- Includes High-Side N-Channel MOSFET Drivers for Charge and Discharge Control:

- Supports Soft-Start to Eliminate Pre-Charge Circuit

- Drives Up to 100A DC with Parallel N-Channel MOSFETs

- Configurable MOSFET Protections with Recovery Option:

- Charge/Discharge OCP and SCP

- Cell UVP and OVP

- Pack UVP and OVP

- Cell Low-/High-Temperature Protection

- Die High-Temperature Protection

- Configurable Fuse Protections

- Cell Dead and SOVP

- Pack SUVP and SOVP

- MOSFET Damage Protection

- Self-Diagnostics Protection

- Passive Cell Balancing up to 58mA per Cell:

- Can Drive External Balancing Transistors

- Automatic or Manual Control

- Additional Features:

- Intelligent Open Wire Detection

- Integrated 3.3V and 5V LDO

- Reduced Current Standby Mode

- Load and Charge Plug-In and Removal Detection

- High-Voltage and Low-Voltage GPIOs

- Configurable for Low-side MOSFET Ctrl

- Dedicated Thermistor Inputs

- Persistent Dead Battery Flag

- Lockable Programmable Memory for Protection Configuration

MP3714 - 3S TO 16S BATTERY MONITOR AND PROTECTOR W/ COULOMB COUNTING

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

- I<sup>2</sup>C or SPI Interface with 8-Bit CRC

- Random Cell Connection Tolerant

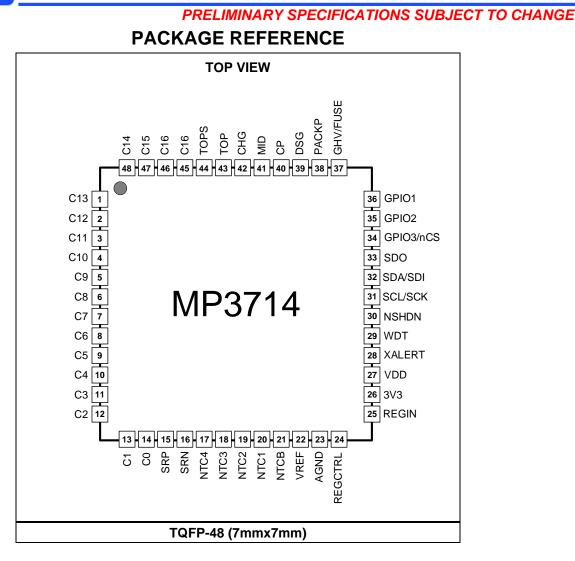

- Available in a TQFP-48 (7mmx7mm) Package

### **APPLICATIONS**

- Energy Storage System (ESS)

- E-Bikes, E-Scooters

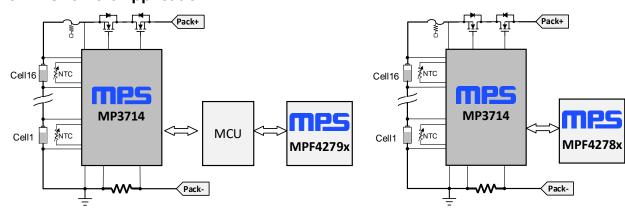

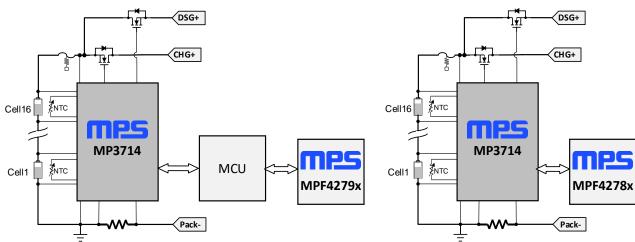

## **TYPICAL APPLICATION**

### MP3714 One Port Application

- Light Electric Vehicles (LEVs)

- Power and Gardening Tools

- Battery Backups and UPS

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

### **MP3714 Separate Port Application**

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

#### **ORDERING INFORMATION**

| Part Number*     | Package              | Top Marking | MSL Rating | Comment                               |

|------------------|----------------------|-------------|------------|---------------------------------------|

| MP3714DFP-xxxx** | TQFP-48<br>(7mmx7mm) | See Below   | 2          |                                       |

| MP3714DFP-0000   | TQFP-48<br>(7mmx7mm) | See Delow   | 3          | I <sup>2</sup> C, 3V3 off in shutdown |

\* For Tray, add suffix -T (e.g. MP3714DFP-xxxx-T).

\* For Tape & Reel, add suffix -Z (e.g. MP3714DFP-xxxx-Z).

\*\* "xxxx" is the configuration code identifier for the register settings. Each "x" can be a hexadecimal value between 0 and F. Contact an MPS FAE to create this unique number.

### **TOP MARKING**

TBD

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

### **PIN FUNCTIONS**

| Pin # | Name      | Туре                                         | Description                                                                                                                                                             |

|-------|-----------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | C13       |                                              | Connect to the positive pin of cell 13.                                                                                                                                 |

| 2     | C12       | I                                            | Connect to the positive pin of cell 12.                                                                                                                                 |

| 3     | C11       | I                                            | Connect to the positive pin of cell 11.                                                                                                                                 |

| 4     | C10       | I                                            | Connect to the positive pin of cell 10.                                                                                                                                 |

| 5     | C9        | I                                            | Connect to the positive pin of cell 9.                                                                                                                                  |

| 6     | C8        |                                              | Connect to the positive pin of cell 8.                                                                                                                                  |

| 7     | C7        | I                                            | Connect to the positive pin of cell 7.                                                                                                                                  |

| 8     | C6        | I                                            | Connect to the positive pin of cell 6.                                                                                                                                  |

| 9     | C5        | I                                            | Connect to the positive pin of cell 5.                                                                                                                                  |

| 10    | C4        | I                                            | Connect to the positive pin of cell 4.                                                                                                                                  |

| 11    | C3        | I                                            | Connect to the positive pin of cell 3.                                                                                                                                  |

| 12    | C2        | I                                            | Connect to the positive pin of cell 2.                                                                                                                                  |

| 13    | C1        | I                                            | Connect to the positive pin of cell 1.                                                                                                                                  |

| 14    | C0        |                                              | Connect to the negative pin of cell 1.                                                                                                                                  |

| 15    | SRP       | I                                            | Positive sense pin.                                                                                                                                                     |

| 16    | SRN       |                                              | Negative sense pin.                                                                                                                                                     |

| 17    | NTC4      |                                              | Thermistor 4 terminal.                                                                                                                                                  |

| 18    | NTC3      | 1                                            | Thermistor 3 terminal.                                                                                                                                                  |

| 19    | NTC2      |                                              | Thermistor 2 terminal.                                                                                                                                                  |

| 20    | NTC1      | 1                                            | Thermistor 1 terminal.                                                                                                                                                  |

| 21    | NTCB      | 0                                            | NTC bias. Connect an external 10nF bypass capacitor from NTCB to AGND.                                                                                                  |

|       |           |                                              | ADC reference voltage. Connect an external 1µF bypass capacitor from                                                                                                    |

| 22    | VREF      | Р                                            | VREF to AGND.                                                                                                                                                           |

|       |           | _                                            | Ground. Connect AGND near the positive connection (SRP) of the low-side                                                                                                 |

| 23    | AGND      | Р                                            | sense resistor.                                                                                                                                                         |

| 24    | REGCTRL   | Р                                            | Turn-on control for external BJT low-dropout (LDO) regulator.                                                                                                           |

| 25    | REGIN     | Р                                            | <b>Internal regulator input.</b> Connect an external 3.3µF bypass capacitor from REGIN to AGND.                                                                         |

| 26    | 3V3       | Р                                            | <b>3.3V voltage output to drive external peripherals.</b> Bypass 3V3 with an external 1µF capacitor.                                                                    |

| 27    | VDD       | Р                                            | <b>1.8V rail for internal use.</b> Connect a 1µF bypass capacitor from VDD to AGND.                                                                                     |

| 28    | XALERT    | 0                                            | Interrupt alert output.                                                                                                                                                 |

| 29    | WDT       | 1/0                                          | Watchdog timer pin.                                                                                                                                                     |

| 30    | NSHDN     | <u>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,</u> | Active-low shutdown input signal.                                                                                                                                       |

|       |           |                                              | <b>Multi-function pin.</b> This pin can be set as the I <sup>2</sup> C interface clock or the SPI                                                                       |

| 31    | SCL/SCK   |                                              | interface clock. This pin is open drain mode.                                                                                                                           |

|       |           |                                              | Multi-function pin. This pin can be set as the I <sup>2</sup> C interface data or the SPI                                                                               |

| 32    | SDA/SDI   | I/O                                          | serial data input. This pin is open drain mode.                                                                                                                         |

| 33    | SDO       | 0                                            | SPI serial data output.                                                                                                                                                 |

|       |           |                                              | Multi-function pin. This pin can be set as General-purpose pin 3 (GPIO3),                                                                                               |

| 34    | GPIO3/nCS | I/O                                          | NTC7, SPI cable selection, fault indication, or auto cell balancing activation.                                                                                         |

| 35    | GPIO2     | I/O                                          | <b>Multi-function pin.</b> This pin can be set as GPIO2, NTC6, CHG MOSFET control, or logic output in phase with DSG for low-side MOSFET control.                       |

| 36    | GPIO1     | I/O                                          | Multi-function pin. This pin can be set as GPIO1, NTC5, DSG MOSFET control, CHG and DSG MOSFETs control, or logic output in phase with CHG for low-side MOSFET control. |

| 37    | GHV/FUSE  | I/O                                          | Multi-function pin. This pin can be set as General-purpose high-voltage pin                                                                                             |

|       |           | - 1/0                                        |                                                                                                                                                                         |

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

### PIN FUNCTIONS (continued)

| Pin # | Name  | Туре | Description                                                                                                                                                                  |

|-------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38    | PACKP | I/O  | Pack sensing voltage (load side).                                                                                                                                            |

| 39    | DSG   | 0    | Discharge MOSFET driver.                                                                                                                                                     |

| 40    | СР    | Р    | <b>Charge pump regulated voltage.</b> Connect a 47nF capacitor from CP to MID, then adjust the value based on the number of parallel DSG and CHG MOSFETs.                    |

| 41    | MID   | Р    | <b>Protection MOSFET middle point.</b> Used as the charge pump supply input and charger insert detection.                                                                    |

| 42    | CHG   | 0    | Charge MOSFET driver.                                                                                                                                                        |

| 43    | TOP   | Р    | <b>Battery stack top, low-current positive supply pin.</b> TOP must be connected to the top of the battery stack, which is the highest positive voltage in the battery pack. |

| 44    | TOPS  | I    | <b>Connect to the positive pin of cell 16.</b> Sample the highest positive voltage in the battery pack.                                                                      |

| 45    | C16   | I    | Connect to the positive pin of cell 16.                                                                                                                                      |

| 46    | C16   | Ι    | Connect to the positive pin of cell 16.                                                                                                                                      |

| 47    | C15   |      | Connect to the positive pin of cell 15.                                                                                                                                      |

| 48    | C14   | Ι    | Connect to the positive pin of cell 14.                                                                                                                                      |

### ABSOLUTE MAXIMUM RATINGS (1)

| CHG, DSG, CP to AGND     | 0.3V to +100V    |

|--------------------------|------------------|

| GHV to AGND              | 0.3V to +86V     |

| GHV to TOP               |                  |

| TOP to AGND              | 0.3V to +86V     |

| PACKP to AGND            | 0.5V to +86V     |

| MID to AGND              |                  |

| Cn - C(n-1) (n: 1 to 16) |                  |

| Cn to AGND (n: 1 to 7)   |                  |

| Cn to AGND (n: 8 to 16)  |                  |

| C0 to AGND               |                  |

| SRP, SRN to AGND         | 0.5V to +6.0V    |

| CP to MID                | 0.3V to +20V     |

| REGCTRL to AGND          | 0.3V to +15V     |

| NSHDN to AGND            |                  |

| VDD to AGND              | 0.3V to +2V      |

| All other pins to AGND   | 0.3V to +6.0V    |

| Junction temperature     | 150°C            |

| Lead temperature         | 260°C            |

| Storage temperature      | - 65°C to +150°C |

### ESD Ratings

| Human body model (HBM) <sup>(2)</sup>     | 1kV  |

|-------------------------------------------|------|

| Charged device model (CDM) <sup>(3)</sup> | 500V |

#### **Recommended Operating Conditions** <sup>(4)</sup>

| TOP voltage                             | 8V to 67.2V     |

|-----------------------------------------|-----------------|

| Cn - C(n-1) (n: 1 to 14) <sup>(5)</sup> | 0.2V to 5V      |

| C0 to AGND                              | 0.25V to +0.3V  |

| REGIN voltage                           | 4.5V to 5.5V    |

| Operating temperature (T <sub>J</sub> ) | 40°C to +125°C  |

| SRP to SRN                              | 100mV to +100mV |

#### Thermal Metrics (6)

| Junction-to-ambient (R <sub>0JA</sub> )          | 46.6°C/W |

|--------------------------------------------------|----------|

| Junction-to-case (top) (R <sub>0JC(TOP)</sub> )  | 14.5°C/W |

| Junction-to-board (top) (R <sub>0JB(TOP)</sub> ) | 27.1°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) Tested per ANSI/ESDA/JEDEC JS-001.

- 3) Tested per ANSI/ESDA/JEDEC JS-002.

- 4) The device is not guaranteed to function outside of its operating conditions.

- 5) The stack voltage should be greater than 8V.

- 6) Metrics provided using set-up conditions compliant with EIA/JESD51-2, 7, and 8.

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.