MP18871

# Isolated PWM-Input Control High-Side/Low-Side Half-Bridge Gate Driver

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## DESCRIPTION

$\bigcirc$  D I C

The MP18871 is an isolated half-bridge gate driver solution with up to 4A source and sink peak current capacity. The gate driver is designed to drive power switching devices with short propagation delay and pulse-width distortion. By utilizing MPS proprietary capacitive-based isolation technology, the driver can provide up to 5kV<sub>RMS</sub> withstand voltage (per UL1577) with SOIC wide-body package and greater than 100kV/µs commonmode transient immunity (CMTI) rating between the input side and output driver. With the advanced features, the drivers operate high efficiency, high power density, and robustness in a wide variety of power applications.

The MP18871 integrates dual-channel gate drivers in one package. Each output can be grounded to the separated grounds or connected to a positive or negative voltage reference. The secondary topology can be configured as a half-bridge high-side/low-side driver controlled by single PWM input signal. To prevent the occurrence of the shoot-through issue in half-bridge driver, the MP18871 provides the programmable dead-time set by an external resister.

A wide primary-side VDDI supply range makes the driver suitable to be interfaced with 3.3V or 5V digital controllers. And the secondary-side driver accepts up to 30V supply. All the supply voltage pins are with various under voltage lock-out (UVLO) level protection.

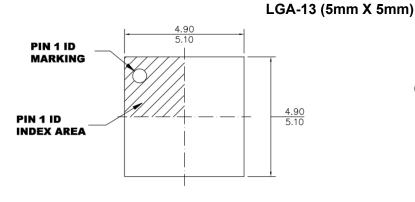

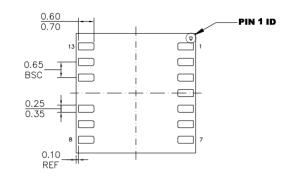

The MP18871 is available in narrow-/wide-body SOIC-16 and LGA-13 5mmx5mm packages.

## FEATURES

- PWM-Input Half-Bridge Driver

- Up to 5kV<sub>RMS</sub> Input to Output Isolation (SOIC-16 WB)

- 1500V<sub>DC</sub> Functional Isolation between Two Secondary-Side Drivers (SOIC-16 NB/WB)

- 700V<sub>DC</sub> Functional Isolation between Two Secondary-Side Drivers (LGA-13 5mmx5mm)

- Common-Mode Transient Immunity (CMTI) >100kV/µs

- 2.8V to 5.5V Input VDDI Range to Interface with TTL and CMOS Compatible Inputs

- Up to 30V Output Drive Supply with Several UVLO Options

- 4A Source, 4A Sink Peak Current Output

- 50ns Typical Propagation Delay

- Overlap Protection and Programmable

Dead-time Control

- Operating Temperature Range -40°C to +125°C

- UL 1577 Certified

- SOIC-16 NB: 3kV<sub>RMS</sub> Isolation for 60 secs.

- SOIC-16 WB: 5kV<sub>RMS</sub> Isolation for 60 secs.

- LGA-13: 2.5kV<sub>RMS</sub> Isolation for 60 secs.

## **APPLICATIONS**

- Half/Full-Bridge Converters

- Isolated DC/DC Converters

- Offline Isolated AC/DC Converters

- DC/AC Inverters

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **SELECTION GUIDE**

| Part Number | Peak<br>Output<br>Current<br>(A) | Output<br>UVLO<br>(V) | On/Off<br>Logic | Input<br>Logic | Configura<br>-tion | Overlap<br>Protection | Programm<br>-able<br>Dead-Time | Package<br>Type      |                      |  |           |  |  |            |

|-------------|----------------------------------|-----------------------|-----------------|----------------|--------------------|-----------------------|--------------------------------|----------------------|----------------------|--|-----------|--|--|------------|

| MP18871-4A  |                                  | 3                     |                 |                |                    |                       |                                |                      |                      |  |           |  |  |            |

| MP18871-4B  |                                  | 5                     |                 | EN PWM /Low-   | High-Side          |                       |                                | SOIC-16 NB           |                      |  |           |  |  |            |

| MP18871-4C  | 4                                | 8                     | EN              |                | PWM /Lov           | /Low-Side             | Y                              | Y                    | SOIC-16 WB<br>LGA-13 |  |           |  |  |            |

| MP18871-4D  |                                  | 10                    |                 |                | Half-Bridge        |                       |                                | (5mmx5mm)            |                      |  |           |  |  |            |

| MP18871-4E  |                                  | 12                    |                 |                |                    |                       |                                |                      |                      |  |           |  |  |            |

| MP18871-A4A |                                  | 3                     |                 |                |                    |                       |                                |                      |                      |  |           |  |  |            |

| MP18871-A4B |                                  | 5                     |                 | 6 PWM          |                    |                       |                                |                      |                      |  | High-Side |  |  | SOIC-16 NB |

| MP18871-A4C | 4                                | 8                     | DIS             |                | /Low-Side          | Y                     | Y                              | SOIC-16 WB<br>LGA-13 |                      |  |           |  |  |            |

| MP18871-A4D |                                  | 10                    |                 |                | Half-Bridge        |                       |                                | (5mmx5mm)            |                      |  |           |  |  |            |

| MP18871-A4E |                                  | 12                    |                 |                |                    |                       |                                |                      |                      |  |           |  |  |            |

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

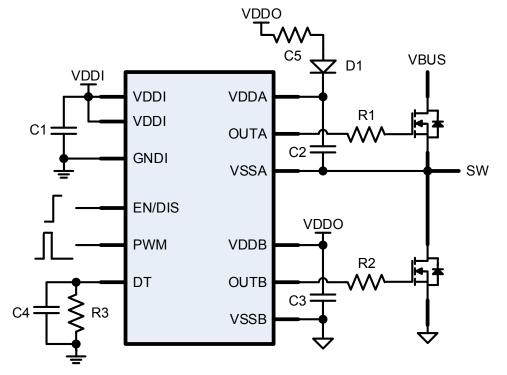

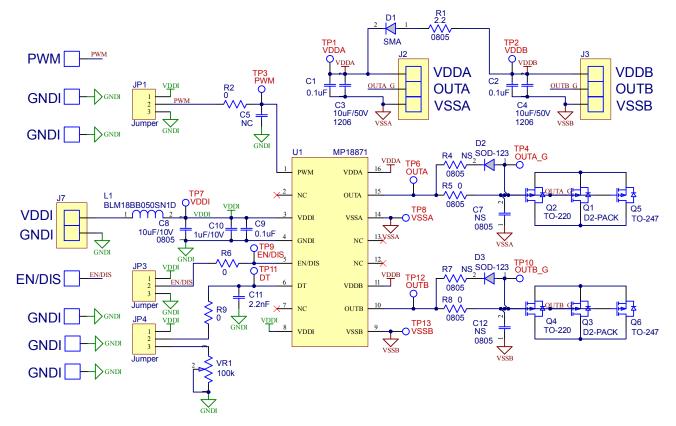

# **TYPICAL APPLICATION**

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# ORDERING INFORMATION

| Part Number*   | Package          | Top Marking | MSL Rating |

|----------------|------------------|-------------|------------|

| MP18871-4AGSE  |                  |             |            |

| MP18871-4BGSE  |                  |             |            |

| MP18871-4CGSE  | SOIC-16 NB       |             | 2          |

| MP18871-4DGSE  |                  |             |            |

| MP18871-4EGSE  |                  |             |            |

| MP18871-4AGY   |                  |             |            |

| MP18871-4BGY   |                  |             |            |

| MP18871-4CGY   | SOIC-16 WB       |             |            |

| MP18871-4DGY   |                  |             |            |

| MP18871-4EGY   |                  |             | 3          |

| MP18871-4AGLU  |                  |             | 5          |

| MP18871-4BGLU  |                  |             |            |

| MP18871-4CGLU  | LGA-13 (5mmx5mm) |             |            |

| MP18871-4DGLU  |                  |             |            |

| MP18871-4EGLU  |                  | See Below   |            |

| MP18871-A4AGSE |                  | See Delow   |            |

| MP18871-A4BGSE |                  |             |            |

| MP18871-A4CGSE | SOIC-16 NB       |             | 2          |

| MP18871-A4DGSE |                  |             |            |

| MP18871-A4EGSE |                  |             |            |

| MP18871-A4AGY  |                  |             |            |

| MP18871-A4BGY  |                  |             |            |

| MP18871-A4CGY  | SOIC-16 WB       |             |            |

| MP18871-A4DGY  |                  |             |            |

| MP18871-A4EGY  |                  |             | 3          |

| MP18871-A4AGLU |                  |             | 5          |

| MP18871-A4BGLU |                  |             |            |

| MP18871-A4CGLU | LGA-13 (5mmx5mm) |             |            |

| MP18871-A4DGLU |                  |             |            |

| MP18871-A4EGLU |                  |             |            |

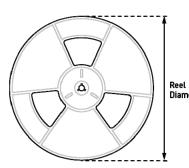

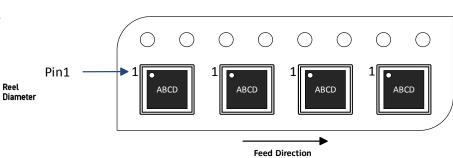

\* For Tape & Reel, add suffix -Z (e.g. MP18871-4AGSE-Z / MP18871-4AGY-Z / MP18871-4AGLU-Z)

Please contact local sales or our distributors to check the latest availability status for the ordering part numbers.

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

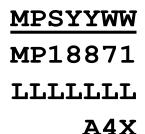

## **TOP MARKING**

MP18871-4X (SOIC-16 NB & SOIC-16 WB)

# MPS YYWW

# M18871-4X

### LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code M18871-4X: Part number X: UVLO level code, where X=A, B, C, D or E LLLLLLLL: Lot number

## **TOP MARKING**

MP18871-A4X (SOIC-16 NB & SOIC-16 WB)

<u>MPS YYWW</u> 18871-A4X

## LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code 18871-A4X: Part number X: UVLO level code, where X=A, B, C, D or E LLLLLLLLL: Lot number

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **TOP MARKING**

MP18871-4X (LGA-13 5mmx5mm)

# MPSYYWW MP18871 LLLLLLL

# 4X

MPS: MPS prefix YY: Year code WW: Week code MP18871: Part number LLLLLLL: Lot number 4X: The rest alphanumeric characters of part number X: UVLO level code, where X=A, B, C, D or E

## **TOP MARKING**

MP18871-A4X (LGA-13 5mmx5mm)

MPS: MPS prefix YY: Year code WW: Week code MP18871: Part number LLLLLLL: Lot number A4X: The rest alphanumeric characters of part number X: UVLO level code, where X=A, B, C, D or E

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

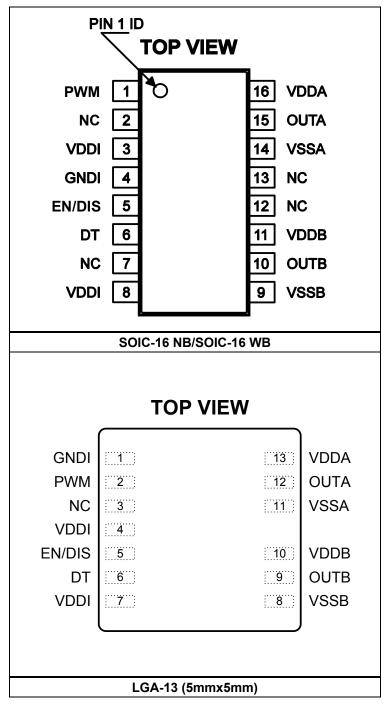

## PACKAGE REFERENCE

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **PIN FUNCTIONS**

| Pin # Name |        | Nama | Description                                                                                                                                                                                                                                                                                           |

|------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOIC-16    | LGA-13 | Name | Description                                                                                                                                                                                                                                                                                           |

| 1          | 2      | PWM  | <b>PWM Logic Control Signal Input.</b> PWM pin can accept a TTL/CMOS level compatible input logic. This pin is internally pulled down to GNDI. OUTA is in phase with PWM input and OUTB is always complementary with OUTA with a programmed dead-time.                                                |

| 3,8        | 4,7    | VDDI | <b>Input-Side Power Supply Input.</b> These two pins are internally shorted. VDDI supplies power to the primary side control circuitry. Locally decoupled to GNDI using a low ESR/ESL bypass capacitor. The capacitor should be placed as close to the chip as possible.                              |

| 4          | 1      | GNDI | <b>Input-Side Ground.</b> Ground reference for all input-side signal and internal control blocks.                                                                                                                                                                                                     |

| 5          | 5      | EN   | <b>Enable Control Input.</b> EN pin can be driven by an external TTL/CMOS level compatible input logic signal to enable/disable the chip. This pin is internally pulled high. Turn on the chip if set high or left open, shutdown the driver output if pulled low.                                    |

| 5          | 5      | DIS  | <b>Disable Control Input.</b> DIS pin can be driven by an external TTL/CMOS level compatible input logic signal to enable/disable the chip. This pin is internally pulled low. Turn on the chip if set low or left open, shutdown the driver output if pulled high.                                   |

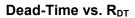

| 6          | 6      | DT   | <b>Dead-Time Programming Input.</b> Leaving DT open sets the dead time to the minimal value. Tie a $2k\Omega$ to $150k\Omega$ resistor between DT and GNDI to program the dead-time. It is recommended to parallel a 220pF or above ceramic capacitor with this resister for improved noise immunity. |

| 2,7,12,13  | 3      | NC   | No Connection.                                                                                                                                                                                                                                                                                        |

| 9          | 8      | VSSB | Output-Side Ground for Driver B. Ground reference for output driver B.                                                                                                                                                                                                                                |

| 10         | 9      | OUTB | Gate Drive Output of Driver B. Connect to the gate of power device in channel B.                                                                                                                                                                                                                      |

| 11         | 10     | VDDB | <b>Output-Side Driver Power Supply Input for Driver B.</b> This pin supplies power to the secondary side driver B circuitry. Locally decoupled to VSSB using a low ESR/ESL bypass capacitor. The capacitor should be placed as close to the chip as possible.                                         |

| 14         | 11     | VSSA | Output-Side Ground for Driver A. Ground reference for output driver A.                                                                                                                                                                                                                                |

| 15         | 12     | OUTA | Gate Drive Output of Driver A. Connect to the gate of power device in channel A.                                                                                                                                                                                                                      |

| 16         | 13     | VDDA | <b>Output-Side Driver Power Supply Input for Driver A.</b> This pin supplies power to the secondary side driver A circuitry. Locally decoupled to VSSA using a low ESR/ESL bypass capacitor. The capacitor should be placed as close to the chip as possible.                                         |

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup>

| VDDI-GNDI                                                | -0.3V to 6.5V                                |

|----------------------------------------------------------|----------------------------------------------|

| V <sub>PWM</sub> , V <sub>EN/DIS</sub> , V <sub>DT</sub> |                                              |

|                                                          | GNDI-0.3V) to (VDDI+0.3V)                    |

| V <sub>PWM</sub> , V <sub>EN/DIS</sub> Transie           | nt for 50ns                                  |

|                                                          | GNDI-5.0V) to (VDDI+0.3V)                    |

| VDDA-VSSA, VDDB                                          | -VSSB0.3V to 35V                             |

|                                                          | SSA-0.3V) to (VDDA+0.3V)                     |

| V <sub>OUTA</sub> Transient for 2                        |                                              |

|                                                          | SSA-2.0V) to (VDDA+0.3V)                     |

|                                                          | SSB-0.3V) to (VDDB+0.3V)                     |

| VOUTB Transient for 2                                    |                                              |

|                                                          | SSB-2.0V) to (VDDB+0.3V)                     |

| VSSA-VSSB                                                |                                              |

|                                                          | 1500V to +1500V                              |

|                                                          | )700V to +700V                               |

|                                                          | issipation (T <sub>A</sub> = +25°C) $^{(2)}$ |

|                                                          |                                              |

|                                                          |                                              |

| · · · · · · · · · · · · · · · · · · ·                    | )1175mW                                      |

|                                                          | e 150°C                                      |

| Lead Temperature                                         |                                              |

| Storage Temperature                                      | e65°C to +150°C                              |

| ESD Patings                                              |                                              |

#### ESD Ratings

| Human body model (HBM)     | . 4kV |

|----------------------------|-------|

| Charged device model (CDM) | . 2kV |

#### **Recommended Operating Conditions**<sup>(3)</sup>

| VDDI-GNDI                                                     |

|---------------------------------------------------------------|

| V <sub>PWM</sub> , V <sub>EN/DIS</sub> GNDI to VDDI           |

| VDDA-VSSA, VDDB-VSSB                                          |

|                                                               |

| 6.5V to 30V (5V UVLO rev.)                                    |

|                                                               |

|                                                               |

| 14.5V to 30V (12V UVLO rev.)                                  |

| Operating Junction Temp. $(T_J)$ 40°C to +125°C               |

| Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$ |

|                  | •JA | -30  |       |

|------------------|-----|------|-------|

| SOIC-16 WB       | 56  | 30   | °C/W  |

| SOIC-16 NB       | 59  | 35   | °C/W  |

| LGA-13 (5mmx5mm) | 106 | . 50 | .°C/W |

#### Notes:

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on MP18871 evaluation board, 2 layer PCB.

<sup>1)</sup> Exceeding these ratings may damage the device.

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## ELECTRICAL CHARACTERISTICS

$2.8V \le VDDI$ -GNDI  $\le 5.5V$ , VDDA-VSSA = VDDB-VSSB = 5V/12V/15V<sup>(5)</sup>, T<sub>J</sub> =  $-40^{\circ}C$  to  $+125^{\circ}C$ , typical value is tested at T<sub>J</sub> =  $+25^{\circ}C$ , all voltages with respect to the corresponding grounds, unless otherwise noted.

| Parameters                                           | Symbol                   | Condition                                                                                               | Min  | Тур | Max                                                                                                                                                                       | Units |

|------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Input Side Supply Voltage                            | •                        |                                                                                                         |      |     |                                                                                                                                                                           |       |

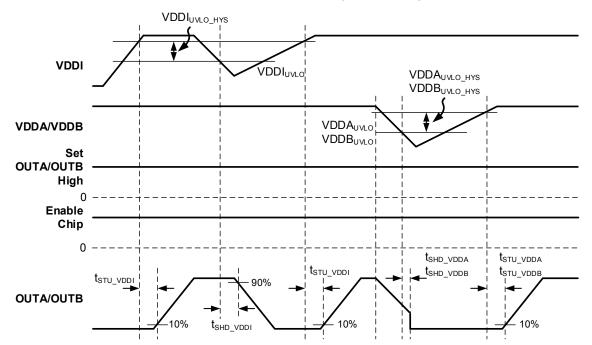

| VDDI Under-Voltage Lockout<br>Threshold              | VDDIuvlo                 | (VDDI-GNDI) falling                                                                                     | 2.42 | 2.6 | 2.78                                                                                                                                                                      | V     |

| VDDI Under-Voltage Lockout<br>Hysteresis             | VDDI <sub>UVLO_HYS</sub> |                                                                                                         | 110  | 135 | 160                                                                                                                                                                       | mV    |

| Input Side Supply Current                            |                          |                                                                                                         |      |     |                                                                                                                                                                           |       |

| VDDI Shutdown Current                                | Ivddi_sd                 | $V_{EN}$ =GNDI or $V_{DIS}$ =VDDI                                                                       |      | 1.0 | 1.3                                                                                                                                                                       | mA    |

| VDDI Operation Current                               | I <sub>VDDI</sub>        | f=500kHz, 50% duty,<br>C <sub>LOAD</sub> =100pF                                                         |      | 2.0 | 2.8                                                                                                                                                                       | mA    |

| Logic Input (PWM, EN/DISABLE)                        |                          |                                                                                                         |      |     |                                                                                                                                                                           |       |

| Logic Input High Threshold                           | V <sub>LI_H</sub>        | (V <sub>LI</sub> -GNDI) rising                                                                          |      | 1.6 | 1.8                                                                                                                                                                       | V     |

| Logic Input Low Threshold                            | V <sub>LI_L</sub>        | (V <sub>LI</sub> -GNDI) falling                                                                         | 1.0  | 1.2 |                                                                                                                                                                           | V     |

| Logic Input Hysteresis Voltage                       | VLI_HYS                  |                                                                                                         | 360  | 400 | 440                                                                                                                                                                       | mV    |

| Internal Pull-Up Resistance                          | R <sub>LI_PU</sub>       | EN                                                                                                      |      | 200 |                                                                                                                                                                           | kΩ    |

| Internal Pull-Down Resistance                        | R <sub>LI_PD</sub>       | PWM, DIS                                                                                                |      | 200 |                                                                                                                                                                           | kΩ    |

| Output Side Supply Voltage                           |                          |                                                                                                         |      |     |                                                                                                                                                                           |       |

|                                                      | VDDAuvlo<br>VDDBuvlo     | -A, 3V threshold                                                                                        | 2.7  | 3.2 | 3.7                                                                                                                                                                       | V     |

| VDDA/VDDB Under-Voltage Lockout<br>Threshold         |                          | -B, 5V threshold                                                                                        | 5    | 5.5 | 6                                                                                                                                                                         | V     |

|                                                      |                          | -C, 8V threshold                                                                                        | 7.5  | 8   | 8.5                                                                                                                                                                       | V     |

| (VDDA-VSSA)/(VDDB-VSSB) falling                      | VDDD0VL0                 | -D, 10V threshold                                                                                       | 9.3  | 10  | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                     | V     |

|                                                      |                          | -E, 12V threshold                                                                                       | 11   | 12  | 13                                                                                                                                                                        | V     |

|                                                      |                          | -A/-B, 3V/5V threshold                                                                                  | 200  | 300 | 400                                                                                                                                                                       | mV    |

| VDDA/VDDB Under-Voltage Lockout                      | VDDA <sub>UVLO_HYS</sub> |                                                                                                         | 420  | 520 | 620                                                                                                                                                                       | mV    |

| Hysteresis                                           | VDDB <sub>UVLO_HYS</sub> | -D/-E,<br>10V/12V threshold                                                                             | 0.8  | 1   | 1.2                                                                                                                                                                       | V     |

| Output Side Supply Current                           |                          |                                                                                                         |      |     |                                                                                                                                                                           |       |

| VDDA/VDDB Shutdown Current                           | Ivdda_sd<br>Ivddb_sd     | V <sub>EN</sub> =GNDI or V <sub>DIS</sub> =VDDI                                                         |      | 1.0 | 1.3                                                                                                                                                                       | mA    |

| VDDA/VDDB Quiescent Current<br>(current per channel) | Ivdda_q<br>Ivddb_q       | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>Set PWM to turn off the<br>corresponding channel |      | 1.0 | 1.3                                                                                                                                                                       | mA    |

| VDDA/VDDB Operation Current                          | Ivdda                    | f=500kHz,<br>C <sub>LOAD</sub> =100pF,<br>VDDA/VDDB=12V                                                 |      | 2.5 | 3.0                                                                                                                                                                       | mA    |

| (current per channel)                                | Ivddb                    | f=500kHz,<br>C <sub>LOAD</sub> =100pF,<br>VDDA/VDDB=15V                                                 |      | 3.0 | 160         1.3         2.8         1.8         440         3.7         6         8.5         10.7         13         400         620         1.2         1.3         1.3 | mA    |

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# ELECTRICAL CHARACTERISTICS (continued)

$2.8V \le VDDI$ -GNDI  $\le 5.5V$ , VDDA-VSSA = VDDB-VSSB = 5V/12V/15V<sup>(5)</sup>, T<sub>J</sub> =  $-40^{\circ}C$  to  $+125^{\circ}C$ , typical value is tested at T<sub>J</sub> =  $+25^{\circ}C$ , all voltages with respect to the corresponding grounds, unless otherwise noted.

| Parameters                                              | Symbol                 | Condition                                                                                 | Min                    | Тур                    | Мах                    | Units |

|---------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-------|

| Gate Driver                                             | •                      |                                                                                           |                        |                        |                        |       |

| Logic High Output Voltage                               | Vouta_h<br>Voutb_h     | I <sub>OUTA/OUTB</sub> =-10mA                                                             | VDDA/<br>VDDB<br>-0.03 | VDDA/<br>VDDB<br>-0.01 |                        | V     |

| Logic Low Output Voltage                                | Vouta_l<br>Voutb_l     | Iouta/outb=10mA                                                                           |                        | VSSA/<br>VSSB<br>+0.01 | VSSA/<br>VSSB<br>+0.03 | V     |

| Output Peak Source Current (6)                          | Iouta_src<br>Ioutb_src | VDDA-VSSA=VDDB-<br>VSSB=15V,<br>VoutA/OUTB-VSSA/VSSB<br>=5V (5V miller plateau)<br>f=1kHz |                        | -4                     |                        | A     |

| Output Peak Sink Current (6)                            | Iouta_snk<br>Ioutb_snk | VDDA-VSSA=VDDB-<br>VSSB=15V,<br>Vouta/OUTB-VSSA/VSSB<br>=5V (5V miller plateau)<br>f=1kHz |                        | 4                      |                        | A     |

| Output Source Resistance                                | Routa_h<br>Routb_h     | Iouta/outb=-10mA                                                                          |                        | 1.3                    | 2.5                    | Ω     |

| Output Sink Resistance                                  | Routa_l<br>Routb_l     | IOUTA/OUTB=10mA                                                                           |                        | 1.0                    | 2.0                    | Ω     |

| Dead-time and Overlap Protection                        |                        |                                                                                           |                        |                        |                        |       |

| Destrict                                                |                        | Leave DT open,<br>(minimum dead-time)                                                     |                        | 10                     | 30                     | ns    |

| Dead-Time                                               | t <sub>DT</sub>        | R <sub>DT</sub> =20kΩ                                                                     | 130                    | 190                    | 250                    | ns    |

|                                                         |                        | $R_{DT}$ =100k $\Omega$                                                                   | 700                    | 900                    | 1100                   | ns    |

| Dead-Time Matching  tdtab-tdtba                         | t <sub>DTM</sub>       |                                                                                           |                        | 0                      | 10                     | ns    |

| Bias Voltage for Dead-Time Set                          | V <sub>DT</sub>        | R <sub>DT</sub> =20kΩ                                                                     | 0.6                    | 0.65                   | 0.7                    | V     |

| DT Resistance Range                                     | Rdt                    |                                                                                           | 2                      |                        | 150                    | kΩ    |

| Switching (Refer to the time seque                      | nce diagram            | for details)                                                                              |                        |                        |                        |       |

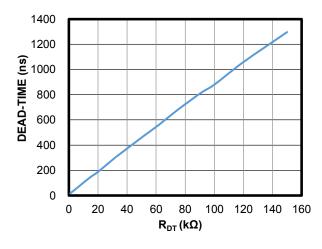

| Output Rise Time                                        | t <sub>R</sub>         | (Vouta/outb-<br>VSSA/VSSB) rising,<br>C <sub>LOAD</sub> =1.8nF                            |                        | 10                     | 20                     | ns    |

| Output Fall Time                                        | t⊧                     | (Vouta/outb-<br>VSSA/VSSB) falling<br>CLOAD=1.8nF                                         |                        | 10                     | 20                     | ns    |

| Minimum Pulse Width                                     | tpw_min                | Output pulse off if<br>shorter than t <sub>PW_MIN</sub> ,<br>C <sub>LOAD</sub> =0pF       |                        | 23                     | 35                     | ns    |

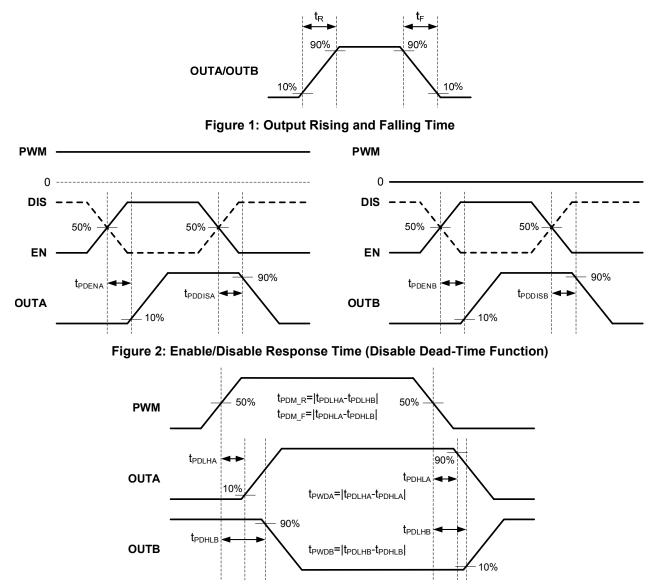

| Propagation Delay from PWM to<br>OUTA/OUTB Rising Edge  | tpdlh                  | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI, C <sub>LOAD</sub> =0pF                | 35                     | 50                     | 65                     | ns    |

| Propagation Delay from PWM to<br>OUTA/OUTB Falling Edge | <b>t</b> PDHL          | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI, C <sub>LOAD</sub> =0pF                | 35                     | 50                     | 65                     | ns    |

MP18871 Rev. 0.8

MonolithicPower.com

10/18/2021 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. Preliminary Specifications Subject to Change © 2021 MPS. All Rights Reserved.

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## ELECTRICAL CHARACTERISTICS (continued)

$2.8V \le VDDI$ -GNDI  $\le 5.5V$ , VDDA-VSSA = VDDB-VSSB =  $5V/12V/15V^{(5)}$ , T<sub>J</sub> =  $-40^{\circ}C$  to  $+125^{\circ}C$ , typical value is tested at T<sub>J</sub> =  $+25^{\circ}C$ , all voltages with respect to the corresponding grounds, unless otherwise noted.

| Parameters                                                                            | Symbol                 | Condition                                                                                                                                                  | Min | Тур | Max | Units |

|---------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Switching (Refer to the time sequer                                                   | nce diagram            | for details)                                                                                                                                               |     |     |     |       |

| Propagation Delay from Enable True<br>to OUTA/OUTB Rising Edge                        | tpden                  | Set OUTA/OUTB<br>outputs high,<br>C <sub>LOAD</sub> =0pF                                                                                                   | 35  | 50  | 65  | ns    |

| Propagation Delay from Disable<br>True to OUTA/OUTB Falling Edge                      | <b>t</b> PDDIS         | Set OUTA/OUTB<br>outputs high,<br>CLOAD=0pF                                                                                                                | 35  | 50  | 65  | ns    |

| Pulse Width Distortion [tpdlh-tpdhl]                                                  | <b>t</b> PWD           | CLOAD=0pF                                                                                                                                                  |     | 1   | 6   | ns    |

| Propagation Delay Matching<br>(Channel-to-Channel)                                    | <b>t</b> PDM           | CLOAD=0pF                                                                                                                                                  |     | 1   | 6   | ns    |

| Startup Delay from Input Supply<br>UVLO Exit to Output Rising Edge                    | tstu_vddi              | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>Set OUTA/OUTB<br>outputs high,<br>C <sub>LOAD</sub> =0pF                                            | 15  | 25  | 35  | μs    |

| Shutdown Delay from Input Supply<br>UVLO Entry to Output Falling Edge <sup>(7)</sup>  | tshd_vddi              | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>Set OUTA/OUTB<br>outputs high,<br>C <sub>LOAD</sub> =0pF                                            |     | 500 |     | ns    |

| Startup Delay from Output Supply<br>UVLO Exit to Output Rising Edge                   | tstu_vdda<br>tstu_vddb | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>Set OUTA/OUTB<br>outputs high,<br>C <sub>LOAD</sub> =0pF                                            | 10  | 20  | 30  | μs    |

| Shutdown Delay from Output Supply<br>UVLO Entry to Output Falling Edge <sup>(7)</sup> | tshd_vdda<br>tshd_vddb | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>Set OUTA/OUTB<br>outputs high,<br>C <sub>LOAD</sub> =0pF                                            |     | 500 |     | ns    |

| Static Common-Mode Transient<br>Immunity <sup>(6)</sup>                               | CMTIstc                | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>V <sub>PWM</sub> =GNDI or VDDI,<br>slew rate of GNDI<br>versus VSSA/VSSB,<br>V <sub>CM</sub> =1500V | 100 |     |     | kV/µs |

| Dynamic Common-Mode Transient<br>Immunity <sup>(6)</sup>                              | CMTI <sub>DYN</sub>    | V <sub>EN</sub> =VDDI or<br>V <sub>DIS</sub> =GNDI,<br>f=100kHz pulse at<br>PWM,<br>slew rate of GNDI<br>versus VSSA/VSSB,<br>V <sub>CM</sub> =1500V       | 100 |     |     | kV/µs |

NOTES:

5) For the test condition, VDDA-VSSA=VDDB-VSSB=5V is used for 3V UVLO devices; VDDA-VSSA=VDDB-VSSB =12V is used for 5V and 8V UVLO devices; VDDA-VSSA=VDDB-VSSB =15V is used for 10V and 12V UVLO devices.

6) Guaranteed by characterization, not production tested.

7) Guaranteed by design.

#### MP18871 Rev. 0.8

#### MonolithicPower.com

10/18/2021 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. Preliminary Specifications Subject to Change © 2021 MPS. All Rights Reserved.

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **INSULATION & SAFETY-RELATED SPECIFICATIONS**

| Parameters                                          | Symbol             | Condition                                                                                                                                                                               | SOIC-16<br>WB | SOIC-16<br>NB     | LGA-13<br>5x5 | Units            |

|-----------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|---------------|------------------|

| External Air Gap<br>(Clearance) <sup>(8)</sup>      | CLR                | Shortest pin-to-pin distance<br>through air between primary and<br>secondary side                                                                                                       | >8            | >4                | 3.5           | mm               |

| External Tracking<br>(Creepage) <sup>(8)</sup>      | CPG                | Shortest pin-to-pin distance across<br>the package surface between<br>primary and secondary side                                                                                        | >8            | >4                | 3.5           | mm               |

| Distance Through<br>Insulation                      | DTI                | Internal Clearance                                                                                                                                                                      | >20           | >20               | >20           | μm               |

| Comparative Tracking<br>Index                       | СТІ                | According to IEC60112                                                                                                                                                                   | >600          | >600              | >600          | V                |

| Material Group                                      |                    | According to IEC 60664-1                                                                                                                                                                | I             | I                 | I             |                  |

| 0 11 0 1                                            |                    | Rated mains voltages ≤ 150V <sub>RMS</sub>                                                                                                                                              | I-IV          | I-IV              | I-IV          |                  |

| Overvoltage Category<br>per IEC 60664-1             |                    | Rated mains voltages ≤ 300V <sub>RMS</sub>                                                                                                                                              | I-IV          | I-III             | I-III         |                  |

|                                                     |                    | Rated mains voltages ≤ 600V <sub>RMS</sub>                                                                                                                                              | -             | -                 |               |                  |

| UL 1577, 5th Ed                                     |                    |                                                                                                                                                                                         |               |                   |               |                  |

| Recognized under UL 157                             | 7 Compor           | nent Recognition Program, Single Pro                                                                                                                                                    | tection. File | e number:         | E322138       |                  |

| Dielectric Withstand<br>Insulation Voltage          | V <sub>ISO</sub>   | $V_{TEST}=V_{ISO}$ for t=60 sec.<br>(qualification),<br>$V_{TEST}=1.2 \times V_{ISO}$ for t=1 sec.<br>(100% production)                                                                 | 5000          | 3000              | 2500          | V <sub>RMS</sub> |

| DIN V VDE V 0884-11: 20                             | 17-01              |                                                                                                                                                                                         |               |                   |               |                  |

| Certified according to DIN                          | V VDE V            | 0884-11 (VDE V 0884-11): 2017-01.                                                                                                                                                       | Certificatio  | n number:         | pending       |                  |

| Maximum Repetitive<br>Peak Isolation Voltage        | VIORM              | AC voltage (bipolar)                                                                                                                                                                    | 891           | 560               | 560           | Vрк              |

| Maximum Working                                     | VIOWM              | AC voltage (sine wave)                                                                                                                                                                  | 630           | 400               | 400           | V <sub>RMS</sub> |

| Isolation Voltage                                   | VIOWM              | DC voltage                                                                                                                                                                              | 891           | 560               | 560           | VDC              |

| Maximum Transient<br>Isolation Voltage              | VIOTM              | V <sub>TEST</sub> =V <sub>IOTM</sub> for t=60 sec<br>(qualification);<br>V <sub>TEST</sub> =1.2 x V <sub>IOTM</sub> for t=1 sec<br>(100% production)                                    | 7071          | 4242              | 3535          | V <sub>PK</sub>  |

| Apparent Charge <sup>(9)</sup><br>Measuring Voltage | V <sub>pd(m)</sub> | Method b1, at routine test (100% production).<br>$V_{pd(ini)}=1.2 \times V_{IOTM}$ , $t_{ini}=1 \sec$ ;<br>$V_{pd(m)}=1.875 \times V_{IORM}$ , $t_m=1 \sec$ ;<br>partial discharge<5 pC | 1697          | 1061              | 1061          | Vрк              |

| Maximum Surge Isolation<br>Voltage <sup>(10)</sup>  | VIOSM              | Tested per IEC 62368-1 with<br>1.2/50µs pulse,<br>V <sub>TEST</sub> =1.3 x V <sub>IOSM</sub> (qualification)                                                                            | 4000          | 4000              | 3500          | Vрк              |

| Barrier Capacitance (11)                            | CIO                | f=1MHz                                                                                                                                                                                  | ~1            | ~1                | ~1            | pF               |

|                                                     |                    | V <sub>IO</sub> =500V, T <sub>A</sub> =25°C                                                                                                                                             |               | >10 <sup>12</sup> |               | Ω                |

| Insulation Resistance (11)                          | R <sub>IO</sub>    | V <sub>IO</sub> =500V, 100°C≤T <sub>A</sub> ≤125°C                                                                                                                                      |               | >1011             |               | Ω                |

|                                                     |                    | V <sub>IO</sub> =500V, T <sub>A</sub> =T <sub>S</sub> =150°C                                                                                                                            |               | >10 <sup>9</sup>  |               | Ω                |

| Pollution Degree                                    |                    | per DIN VDE 0110, Table 1                                                                                                                                                               |               | 2                 |               |                  |

| Climatic Category                                   |                    |                                                                                                                                                                                         |               | 40/125/21         |               |                  |

MP18871 Rev. 0.8

MonolithicPower.com

10/18/2021

MPS Proprietary Information.

Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

Preliminary Specifications Subject to Change

© 2021 MPS. All Rights Reserved.

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

#### NOTES:

- Refer to package information for detailed dimensions. As isolated solution, the recommended land pattern is helpful to keep enough safety creepage and clearance distances on a printed-circuit board.

- 9) Electrical discharge caused by a partial discharge in the coupler.

The primary side terminals as well as the secondary side terminals of the barrier are connected together forming a two-terminal device. Then C<sub>10</sub> and R<sub>10</sub> are measured between the two terminals of the coupler.

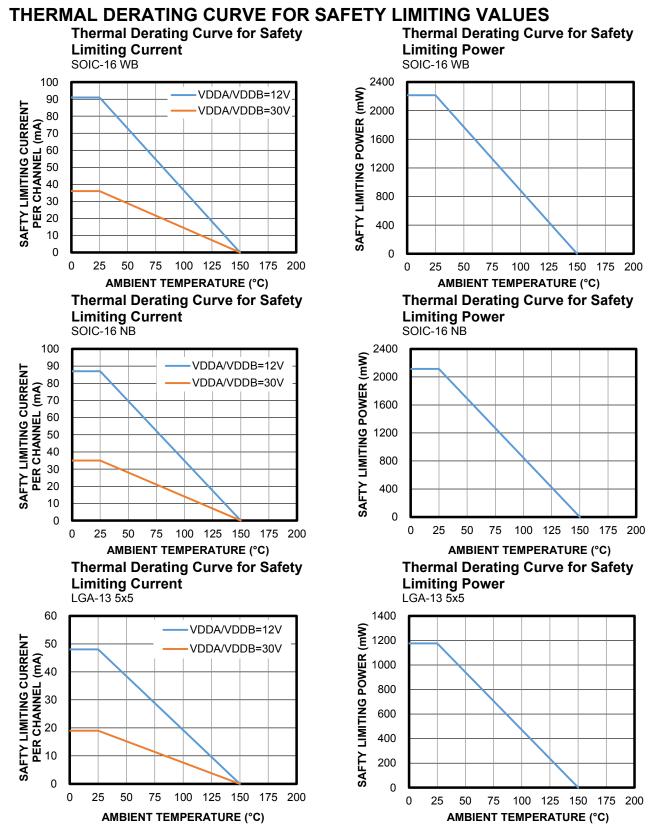

## SAFETY LIMITING VALUES (12)

| Parameters                                    | Symbol | Condition                                                                                    | SOIC-16<br>WB | SOIC-16<br>NB | LGA-13<br>5x5 | Units |

|-----------------------------------------------|--------|----------------------------------------------------------------------------------------------|---------------|---------------|---------------|-------|

| Maximum Safety<br>Temperature <sup>(13)</sup> | Ts     |                                                                                              | 150           | 150           | 150           | °C    |

| Maximum Output Safety<br>Current              | ls_o   | VDDA-VSSA=VDDB-VSSB<br>=12V <sup>(14)</sup> ,<br>T <sub>J</sub> =150°C, T <sub>A</sub> =25°C | 91            | 87            | 48            | mA    |

| (current per channel)                         |        | VDDA-VSSA=VDDB-VSSB=30V,<br>TJ=150°C, TA=25°C                                                | 36            | 35            | 19            | mA    |

|                                               |        | Input side                                                                                   | 15            | 15            | 15            | mW    |

| Safety Power Dissipation                      | D-     | Output side, channel A                                                                       | 1100          | 1050          | 580           | mW    |

| (15)                                          | Ps     | Output side, channel B                                                                       | 1100          | 1050          | 580           | mW    |

|                                               |        | Total                                                                                        | 2215          | 2115          | 1175          | mW    |

NOTES:

13) The maximum safety temperature T<sub>S</sub> has the same value as the maximum junction temperature T<sub>J</sub> (MAX) specified in ABSOLUTE MAXIMUM RATINGS.

14) Tested for 5V and 8V UVLO devices

15) Test condition: VDDI-GNDI=5.5V, VDDA-VSSA=VDDB-VSSB=30V, TJ=150°C, TA=25°C.

The safety power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ :

$T_s=T_J(MAX)=T_A+(\theta_{JA} \times P_S),$

$P_S=I_S \times V_I$ , where  $V_I$  is the input voltage

<sup>10)</sup> Surge test is carried out in oil.

<sup>12)</sup> Maximum value allowed in the event of a failure.

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **MPS**

#### MP18871 - ISOLATED PWM-INPUT HALF-BRIDGE GATE DRIVER

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

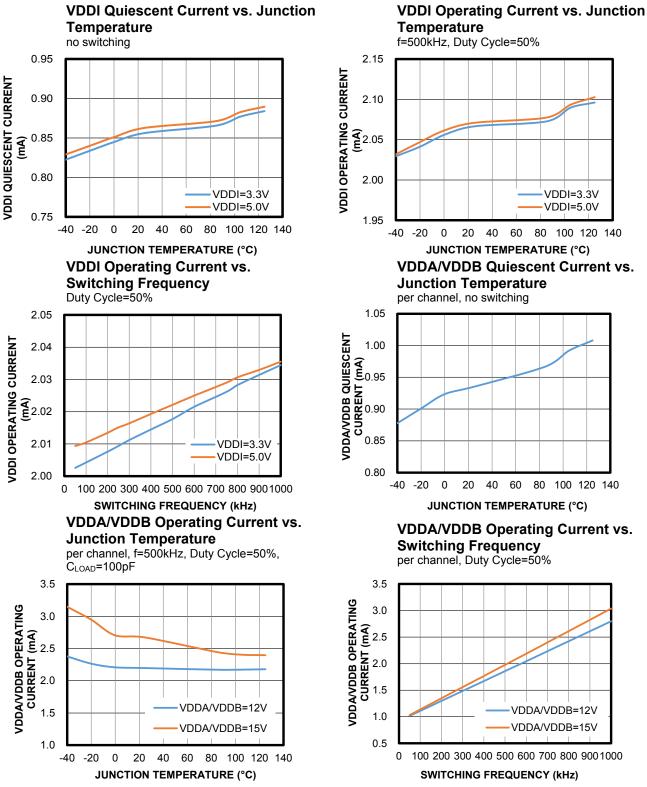

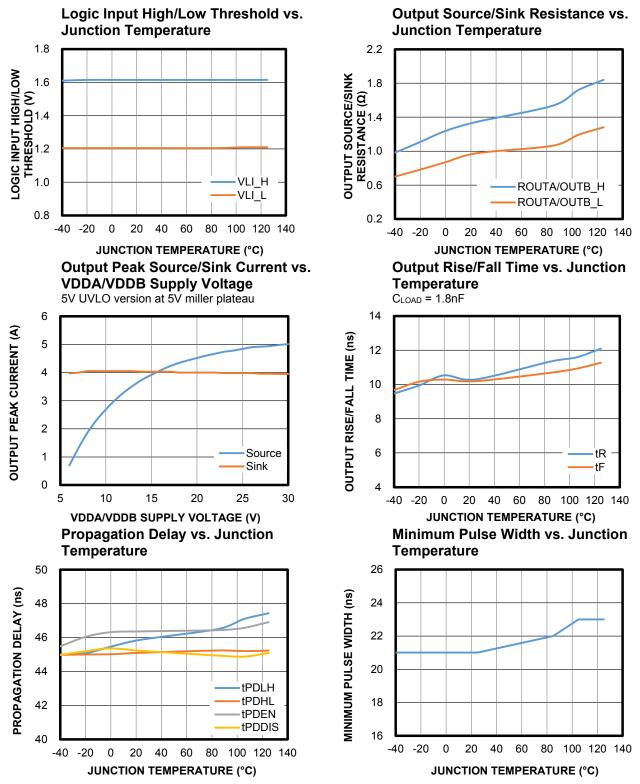

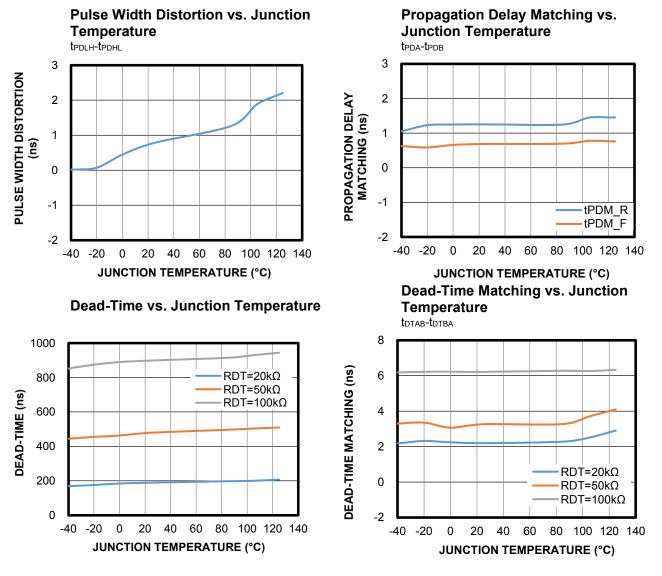

## **TYPICAL CHARACTERISTICS**

VDDI-GNDI = 5V, VDDA-VSSA = VDDB-VSSB = 12V,  $C_{LOAD}$ =0pF,  $T_J$  = 25°C, all voltages with respect to the corresponding grounds, unless otherwise noted.

MP18871 Rev. 0.8 10/18/2021 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. Preliminary Specifications Subject to Change © 2021 MPS. All Rights Reserved.

# **MPS**

#### MP18871 – ISOLATED PWM-INPUT HALF-BRIDGE GATE DRIVER

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# TYPICAL CHARACTERISTICS (continued)

VDDI-GNDI = 5V, VDDA-VSSA = VDDB-VSSB = 12V,  $C_{LOAD}$  = 0pF,  $T_J$  = 25°C, all voltages with respect to the corresponding grounds, unless otherwise noted.

MP18871 Rev. 0.8 10/18/2021 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. Preliminary Specifications Subject to Change © 2021 MPS. All Rights Reserved.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## TYPICAL CHARACTERISTICS (continued)

VDDI-GNDI = 5V, VDDA-VSSA = VDDB-VSSB = 12V,  $C_{LOAD}$  = 0pF,  $T_J$  = 25°C, all voltages with respect to the corresponding grounds, unless otherwise noted.

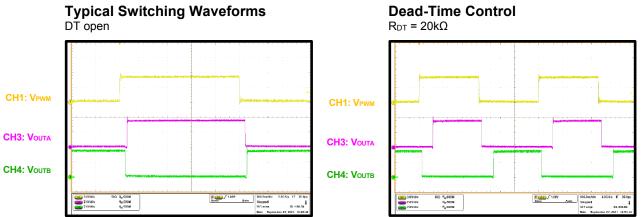

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Performance waveforms are tested on the evaluation board.

VDDI-GNDI = 5V, VDDA-VSSA = VDDB-VSSB = 12V,  $C_{LOAD}=0pF$ ,  $T_A = 25^{\circ}C$ , all voltages with respect to the corresponding grounds, unless otherwise noted.

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **DEFINITIONS OF DYNAMIC PARAMETERS**

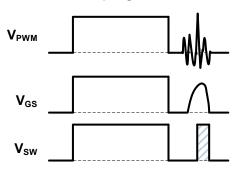

Figure 3: Propagation Delay Matching and Pulse Width Distortion (Disable Dead-Time Function)

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **DEFINITIONS OF DYNAMIC PARAMETERS** (continued)

Figure 4: VDDI and VDDA/VDDB Under-Voltage Lockout (UVLO) (Disable Dead-Time Function)

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **DEVICE FUNCTIONAL MODES**

| Inputs |        |        | Power Supply |      |      | Outputs |      | Notes                              |  |

|--------|--------|--------|--------------|------|------|---------|------|------------------------------------|--|

| PWM    | EN     | DIS    | VDDI         | VDDA | VDDB | OUTA    | OUTB | Noles                              |  |

| L or O | H or O | L or O | Р            | Р    | Р    | L       | Н    | Output transition occurs after the |  |

| н      | H or O | L or O | Ρ            | Ρ    | Ρ    | Н       | L    | dead-time expires.                 |  |

| Х      | L      | Н      | Р            | Х    | Х    | L       | L    | Disable chip                       |  |

| Х      | Х      | Х      | UP           | Х    | Х    | L       | L    | VDDI is unpowered                  |  |

| L or O | H or O | L or O | Ρ            | UP   | Р    | L       | Н    | · VDDA is unpowered                |  |

| Н      | H or O | L or O | Ρ            | UP   | Р    | L       | L    |                                    |  |

| L or O | H or O | L or O | Ρ            | Р    | UP   | L       | L    | VDDB is unpowered                  |  |

| Н      | H or O | L or O | Р            | Р    | UP   | Н       | L    |                                    |  |

#### Table 1: Logic True Table (16)(17)

NOTES:

16) L: Logic Low; H: Logic High; O: Left Open; X: Irrelevant; P: Powered; UP: Unpowered, UVLO condition.

17) If VDDI is powered, the output can operate functionally as long as this channel is powered normally.

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

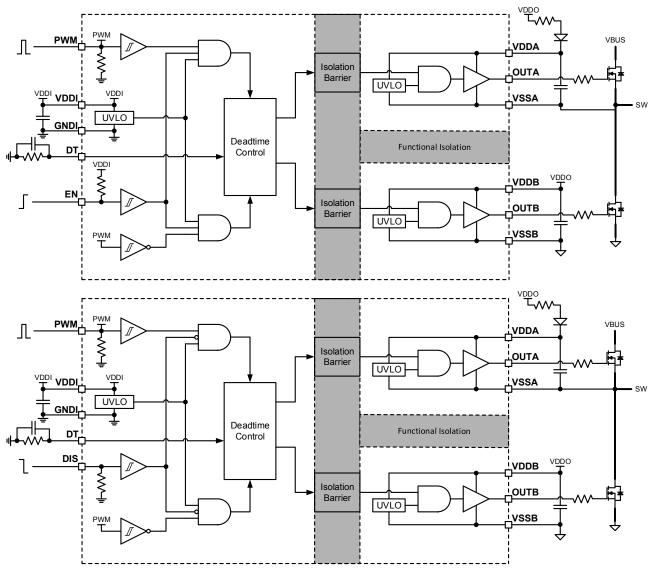

## **BLOCK DIAGRAM**

Figure 6: Functional Block Diagram

## **OPERATION**

The MP18871 is an isolated PWM-input control, half-bridge gate driver solution with 4A peak output current capacity. This IC is designed to drive power switching devices with short propagation delay and pulse-width distortion. With the advanced features, the MP18871 operates high efficiency, high power density, and robustness in a wide variety of power applications.

# Please see Table 1 for whole device functional modes.

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) is implemented to avoid the chip or some blocks from operating at insufficient supply voltage. The MP18871 incorporates the internal UVLO comparators for all input and output supply circuit blocks to monitor VDDI, VDDA and VDDB, respectively. Figure 4 shows the input and output supply UVLO time sequence diagram.

If the input bias voltage VDDI is unpowered or under supply UVLO level, the chip is not activated and the output stages does not receive the control signal from the input stage. Then the UVLO mechanism holds the output forced low, regardless of the present logic levels of the input signals (including EN/DIS and PWM).

When either output stage of the driver is unpowered or below UVLO level, the corresponding channel's output is also pulled low. As long as either channel is powered normally, the corresponding channel can accept the related control signal functionally.

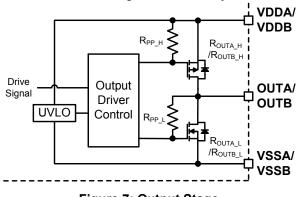

#### Figure 7: Output Stage

#### Input Stage and On/Off Control

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

All of the control input pins (EN/DIS and PWM) accept a TTL/CMOS compatible logic inputs that is reliably isolated from each output. These control pins are easy to be driven with common logic-level signals from a digital controller. But, any input signal applied to these control pins must never be at a higher level than the input stage supply VDDI. So, it is recommended to tie VDDI to the same power supply of the control signal sources. The control logic of EN are active-high while the control logic of DIS are active-low. OUTA is in phase with PWM input and OUTB is always complementary with OUTA.

If the PWM input is left open, it is forced logic low thru the internal pull-down resistor. Provide a determined control signal to PWM pin for stable operation and do not let it floating.

Similarly, for on/off control, the EN pin is tied to VDDI thru the internal pull-up resistor while the DIS pin is connected to GNDI thru the internal pull-down resistor. Although leaving EN/DIS pin floating enables the chip to operate normally after start-up, it is still recommended to provide stable external signal input for on/off control in actual applications.

#### **Output Stage**

The output stage comprises an upper Pchannel MOSFET and a lower N-channel MOSFET (refer to Figure 7). The effective output pull-up source resistance  $R_{OUTA_H}/R_{OUTB_H}$  is the on-resistance of the upper P-channel MOSFET, which delivers the large peak source current during the external power-switch turn-on transition. The pull-down structure is simply an N-channel MOSFET, whose on-resistance  $R_{OUTA_L}/R_{OUTB_L}$  is the output effective pull-down impedance during the drive-low state of the device.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

The output stage is optimized to provide strong driving capacity to a power device during the miller plateau interval of the switching on/off procedure. So the MP18871 is capable of delivering 4A peak source/sink current pulses. And the rail-to-rail output ensures the voltage swings between VDDA/VDDB and VSSA/VSSB, respectively.

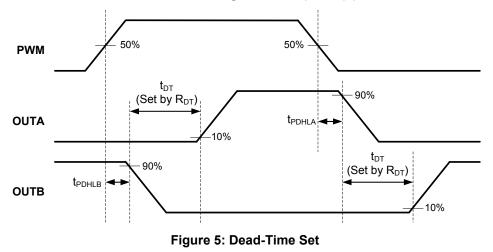

# Programmable Dead-Time and Overlap Protection

To prevent the occurrence of the shoot-through issue in half-bridge driver, the MP18871 allows the user to adjust dead-time (DT), which inserts a user-programmable delay between transitions of OUTA and OUTB. The MP18871 always selects the driver's programmed dead-time as the operating dead-time.

When the dead-time control is enabled, in the meanwhile, the overlap protection scheme is activated. It prevents both channels from outputting logic-high synchronously. This overlap protection doesn't affect the dead-time setting of normal operation.

The dead-time delay operation is present on all output transitions from low to high. Refer to Figure 5 for more information about the operation of dead-time mechanism.

The chip's dead-time is set thru the DT pin. An around 0.65V steady-state bias voltage is generated at DT pin, and the DT pin's source current is monitored to adjust the dead-time delay. When leave DT pin open, a minimum dead-time duration  $(t_{DT})$  is set. Normally, the dead-time is programmed by placing a single resistor  $R_{DT}$  connected from the DT pin to input stage's ground GNDI. This  $R_{DT}$  resistance should be between the values of  $2k\Omega$  and  $150k\Omega$  and a filter capacitor of 220pF or above in parallel is recommended. The curve of the dead-time vs.  $R_{DT}$  is illustrated in TYPICAL PERFORMANCE CHARACTERISTICS.

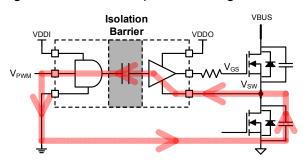

#### **Common-Mode Transient Immunity**

Common-Mode Transient Immunity (CMTI) is one of the key characteristics that correlate to an isolator's robustness, especially important in high-voltage applications with fast transient devices (like SiC/GaN FET). When a power device is switching, the high slew rate dv/dt or di/dt transient noise can corrupt the signal transmission across the isolation barrier. CMTI is defined as maximum tolerable rate-of-rise (or fall) of a common-mode voltage applied between two isolated circuits, given in volts per second (V/ns or  $kV/\mu s$ ). Below the maximum slew rate of a common mode voltage, the output of the isolator remains at the specific logic level and at the specified timing.

Figure 8: High Slew Rate Transient Noise Coupling Path

#### Figure 9: Abnormal Pulse Caused by Coupled Noise if dv/dt > CMTI

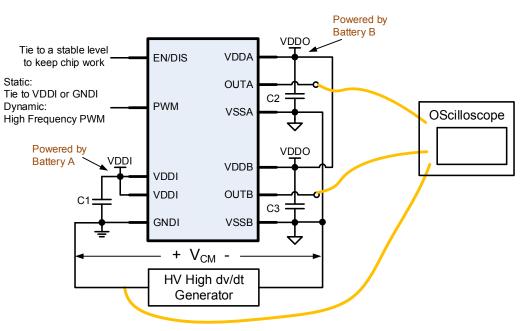

Figure 10 shows the CMTI test setup to measure the CMTI of a coupler in both static and dynamic operation, under specified common-mode pulse magnitude ( $V_{CM}$ ) and specified slew rate of the common-mode pulse ( $dV_{CM}/dt$ ) and other specified test or ambient conditions. The isolator's output should stay in the correct state as long as the pulse magnitude and the slew rate meet the CMTI specification.

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

Figure 10: CMTI Test Setup

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **APPLICATION INFORMATION**

Figure 13 is a reference design for typical application circuit.

#### Selecting the VDDI Capacitor

The input supply VDDI capacitor reduces the surge current drawn from the input supply and supports the current consumption for the primary logic interface and transmitter block. Since the input side's operating current is only a few mA, a 100nF ceramic capacitor with X5R or X7R dielectrics is highly recommended because of its low ESR and small temperature coefficients. For most applications, add a >1 $\mu$ F capacitor in parallel with this 100nF as the bypass capacitor if the real supply power is far away from the VDDI pin.

#### Selecting the VDDA/VDDB Capacitor

As the bypass capacitor of the output gate driver, besides the consumption of driving control block, the VDDA/VDDB capacitor maintains the stable driving voltage and supports up to 4A the transient source current.

Assume the allowable VDDA/VDDB voltage ripple is  $\Delta$ VDDA/VDDB which guarantees that the driver supply voltage cannot drop close to UVLO level, the minimum VDDA/VDDB capacitor is

$$C_{VDDA/VDDB} = \frac{I_{VDDA/VDDB} \times \frac{1}{f_{SW}} + Q_{G}}{\Delta VDDA/VDDB}$$

(1)

where,

$I_{VDDA/VDDB}$  is VDDA/VDDB operation current; f<sub>SW</sub> is the switching frequency;  $Q_G$  is the gate charge of the power device.

Care should be taken when the loop resistance, voltage drop and DC bias voltage ripple have impact on supply voltage. Especially for channel A which usually operates as the high-side driver in a half-bridge converter and is powered by a bootstrap circuity, too large VDDA capacitor is not a good option. It may not be charged fast at system power-up or bootstrap cycle. VDDA could stay below UVLO level and fails to power the high-side driver. Generally, a  $1\mu$ F capacitor is chosen for channel A. If channel A is powered by a special supply, a larger VDDA capacitor can be selected.

Channel B is powered by a special supply and the VDDB capacitor needs to support the VDDA capacitor's charging current thru bootstrap, so a large bypass capacitor can be chosen, like a  $10\mu$ F ceramic capacitor. Similarly, a secondary high frequency bypass capacitor of 100nF in parallel is recommended.

# Selecting the Bootstrap Diode and Series Resistor

A bootstrap configuration is often applied to power the high-side driver in a half-bridge converter. The bootstrap capacitor is charged thru the bootstrap diode and series resistor during the low-side turn-on interval. And the diode needs to load the high reverse voltage (higher than bus voltage) during the low-side turn-on interval. To reduce the conduction losses and reverse recovery losses, a highvoltage, fast recovery diode or schottky diode should be chosen.

Meanwhile, a bootstrap series resistor is also used to limit the inrush charging current, which could generate a spike on VDDA pin. The recommended value is not larger than  $10\Omega$ . Then the estimated peak charging current is

$$I_{BST} = \frac{VDDA / VDDB - V_{D_BST}}{R_{BST}}$$

(2)

where,

$V_{D_BST}$  is the forward voltage drop of the bootstrap diode;

$R_{\mbox{\scriptsize BST}}$  is the bootstrap series resistor.

#### Selecting the Input Filter for PWM

Theoretically, the PWM input filter is not necessary. The low pass filter slows the PWM signal's rising/falling edge and affects the propagation delay. However, it is still recommended to add a simply RC filter at input close to PWM pin if the high frequency ringing introduced by PCB traces is terrible.

Generally, to avoid increasing the input resistance, a smaller than  $100\Omega$  resistor can be selected. When selecting the filter capacitor, make sure the filter's cut-off frequency is at least ten times higher than the switching frequency, a dozens of PF capacitor should be enough.

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

#### Selecting the External Driving Resistor

The external driving resistor can be applied to limit the ringing noise on driving signal and adjust the switching speed to improve EMI resistor performance. But large driving increases the switching losses, reduces system efficiency and brings thermal issue. In actual applications, the turn-on and turn-off speeds can be adjusted by different driving resistors, respectively. The sink resistor is in series with an anti-parallel diode to be separated from the source resistor. And the total driving resistor when pulling down the power device is the sink resistor in parallel with the source resistor.

The peak driving current is the key feature to evaluate the effect of the driving resistors. Without driving resistor, the MP18871 can drive both 4A peak source/sink current.

Considering the driving resistor, the peak source driving current is

$$I_{OUTA\_SRC} = \frac{VDDA}{R_{OUTA\_H} + R_{G\_SRC} + R_{G(int)}}$$

(3)

$$I_{OUTB\_SRC} = \frac{VDDB}{R_{OUTB\_H} + R_{G\_SRC} + R_{G(int)}}$$

(4)

The peak sink driving current is

$$I_{OUTA\_SNK} = \frac{V_{GSA\_ON}}{R_{OUTA\_L} + R_{G\_SRC} \parallel R_{G\_SNK} + R_{G(int)}}$$

(5)

$$I_{OUTB\_SNK} = \frac{R_{GBB\_ON}}{R_{OUTB\_L} + R_{G\_SRC} \parallel R_{G\_SNK} + R_{G(int)}}$$

(6)

where,

$R_{G_{SRC}}$  is the external source resistor;  $R_{G_{SNK}}$  is the external sink resistor;

$R_{G(int)}$  is internal gate resistance of the power device;

$V_{GSA_ON}/V_{GSB_ON}$  is the stable gate-source voltage of the power device in ON interval. Generally, it should be close to VDDA/VDDB.

Since the driving current cannot higher than 4A, select the smaller value of the estimated I<sub>OUTA\_SRC/OUTB\_SRC</sub> or I<sub>OUTA\_SNK/OUTB\_SNK</sub> and 4A as the actual peak driving current.

#### Setting the Dead-Time on DT pin

In half-bridge power converter, a dead-time is inserted during dynamic switching transition between high-side and low-side power devices to prevent shoot-through. The MP18871's dead-time can be controlled by DT setting. The chip always selects the driver's programmed dead-time as the operating dead-time.

The dead-time setting needs to be determined by actual system requirements. By observing the real  $V_{GS}$ ,  $V_{DS}$  and switch node's waveforms of both high-/low-side devices and considering ZVS control logic. Make sure the dead-time interval is with enough margin at any load condition.

The MP18871's dead-time setting is programmed by DT pin. Select the suitable resistor according to the curve of the dead-time vs.  $R_{DT}$ .

#### **Estimate Gate Driver's Power Loss**

The total power loss on the gate driver is used to estimate the thermal performance. The MP18871 needs to operate under Safety Limiting Values.

The first element is the chip's operation power consumption  $P_{OP}$ :

$$P_{OP} = VDDI \times I_{VDDI} + VDDA \times I_{VDDA} + VDDB \times I_{VDDB}$$

(7)

The driver self-power consumption is related to the switching frequency and supply voltage. Typical Characteristics provide the relationship reference of input and output channels' current consumption vs. operating frequency.

The key element is the driving power loss at switching operation. As a conventional totempole gate driver, the MP18871's each channel charges and discharges the gate capacitance of the power device one time during every switching cycle.

During the charging and the discharging period, the total energy is supplied by VDDA/VDDB. If there is no external gate driving resistor, the equation of power dissipation is given as

<sup>10/18/2021</sup> MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. Preliminary Specifications Subject to Change © 2021 MPS. All Rights Reserved.

# mps

#### MP18871 – ISOLATED PWM-INPUT HALF-BRIDGE GATE DRIVER

$$\mathsf{P}_{\mathsf{SW}} = \left(\mathsf{VDDA} \times \int_{0}^{t_{\mathsf{ON}}} i_{\mathsf{GA}}(t) dt + \mathsf{VDDB} \times \int_{0}^{t_{\mathsf{ON}}} i_{\mathsf{GB}}(t) dt\right) \times f_{\mathsf{SW}}$$

$$= (VDDA + VDDB) \times Q_{G} \times f_{SW}$$

(8)

where,

$t_{ON}$  is the turn-on time;  $i_{GA/GB}(t)$  is the driving current.

If the driving current is not saturated to 4A in whole switching cycle with external gate resistors, this power dissipation is shared between the internal source/sink resistances of the gate driver and the external gate driving resistors based on the ratio of these series resistances (see Equation 9).

$$P_{SW} = \frac{VDDA \times Q_{G} \times f_{SW}}{2} \times \left( \frac{R_{OUTA\_H}}{R_{OUTA\_H} + R_{G\_SRC} + R_{G(int)}} + \frac{R_{OUTA\_L} + R_{G\_SRC} \parallel R_{G\_SNK} + R_{G(int)}}{R_{OUTA\_L} + R_{G\_SRC} \parallel R_{G\_SNK} + R_{G(int)}} \right)$$

$$+ \frac{VDDB \times Q_{G} \times f_{SW}}{2} \times \left( \frac{R_{OUTB\_H}}{R_{OUTB\_H} + R_{G\_SRC} + R_{G(int)}} + \frac{R_{OUTB\_L}}{R_{OUTB\_L} + R_{G\_SRC} \parallel R_{G\_SNK} + R_{G(int)}} \right)$$

$$P_{SW\_SAT} = 4A \times \int_{0}^{t_{ON\_SAT}} (VDDA - V_{GSA}(t)) dt + 4A \times \int_{0}^{t_{OFF\_SAT}} (V_{GSA}(t)) dt + 4A \times \int_{0}^{t_{OFF\_SAT}} (V_{GSB}(t)) dt$$

$$+ 4A \times \int_{0}^{t_{ON\_SAT}} (VDDB - V_{GSB}(t)) dt + 4A \times \int_{0}^{t_{OFF\_SAT}} (V_{GSB}(t)) dt$$

$$(9)$$

where,

$t_{ON\_SAT/OFF\_SAT} \ \ is \ \ the \ \ turn-on/off \ \ time \ \ with \ \ saturated \ \ 4A \ \ current \ \ output; \ \ V_{GSA/GSB}(t) \ \ is \ \ the \ \ gate \ \ voltage \ \ of \ \ the \ \ power \ \ device \ \ in \ these \ saturation \ time.$

In some conditions, the MP18871 outputs the saturated 4A current at the beginning of the turn-on/off interval. It results in the power loss calculation in these saturation time becomes Equation 10.

The actual power loss should be the combination of Equation 9 and Equation 10. Then the total power loss dissipated in the MP18871 is

$$P_{\text{LOSS}} = P_{\text{OP}} + P_{\text{SW}} \tag{11}$$

Taking the total power loss multiplied by Junction-to-Ambient Thermal Resistance  $\theta_{JA}$  to know the junction temperature rise above the ambient temperature. Make sure the junction temperature  $T_J$  is below the maximum safety temperature  $T_S$ .

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

#### **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. For best results, refer to the guidelines below.

- Place the bypass/decoupling capacitors as close as possible to the VDDI/VDDA/VDDB supply pins and the corresponding grounds. For each supply pin, it is recommended to add a low ESR/ESL, high frequency bypass capacitor of 100nF.

- 2. Place the dead-time setting resistor and its bypassing capacitor close to DT pin.

- 3. If input RC filter is used, it is recommended to place this filter close to the corresponding control pin.

- 4. Place the high current paths, like supply path, drive path and the connection between the source of the external power device and VSSA/VSSB pin very close to the driver chip with short, direct, and wide traces to minimize the parasitic inductances and avoid large transient and ringing noise.

- 5. It is highly recommended to place large power and ground planes or multiple layers to help dissipate heat from the gate driver chip to PCB to improve the thermal performance. However, must take care of splitting the traces or coppers to allow sufficient insulation distance between different low-/high-voltage planes.

- Keep the driving loop, form OUTA/OUTB, the gate-to-source of the power device to VSSA/VSSB, short in a minimal area. Try to avoid the driving trace across different PCB layers thru vias, since it can bring parasitic inductances. Meanwhile, the driver IC should be placed as close as possible to the power device.

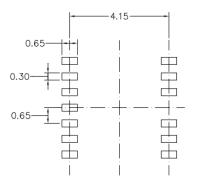

- 7. Refer to the recommended land pattern design of each package type for adequate insulation space between the primary and secondary side. Avoid placing any components, tracks or copper below the chip's body in any PCB layer.

- A board cutout under the chip is not necessary, but it is still recommended to create it to extend the creepage distance on PCB surface, except for small size LGA

package. The LGA package's bottom side is pressed on the PCB surface, so the PCB cutout is not effective but can make the board easy to be twisted.

9. If the driver chip is used in half-bridge configuration, keep enough space and try to increase creepage distance between dual channels.

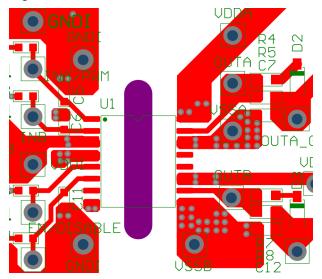

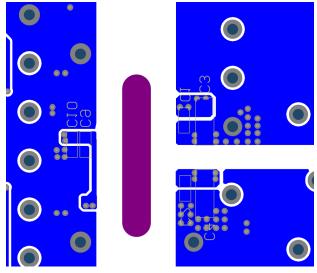

Take a 2-layer PCB layout with SOIC-16 WB package as an example. Figure 11 and 12 shows the layout around the chip. The components labels are consistent with those in Figure 13.

Figure 11: Top Layer Layout Reference

Figure 12: Bottom Layer Layout Reference

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **TYPICAL APPLICATION CIRCUITS**

Figure 13: Typical Application Circuit Reference Design

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

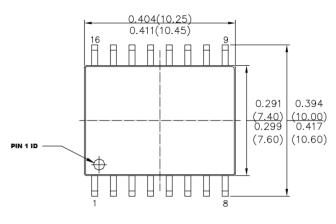

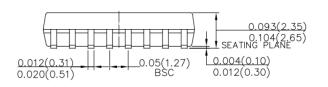

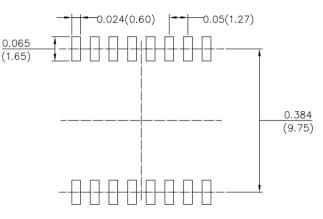

## PACKAGE INFORMATION

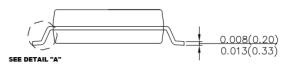

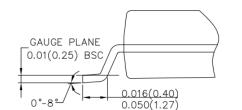

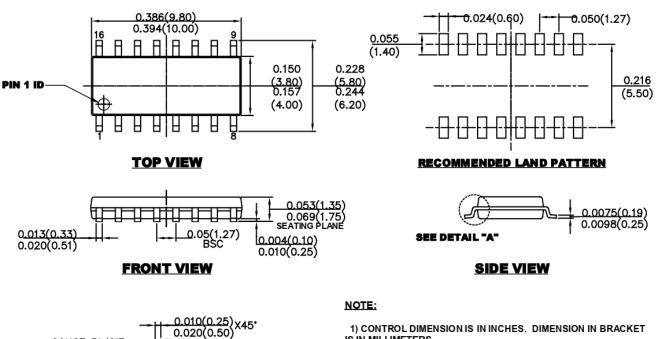

#### SOIC-16 WB (HV ISOLATION)

TOP VIEW

#### FRONT VIEW