# ZipWirePlus™ M28976 G.shdsl Transceiver G.shdsl Dual-Bearer Multi-Mode Transceiver

# M28976

## Two Full-Rate T1/E1 Payloads Over a Single G.shdsl/HDSL2/SDSL Link

#### **Dual-Bearer Operation**

The M28976 includes two independent full-rate T1/E1 interfaces, capable of simultaneously carrying two separate time-synchronized pulse code modulation (PCM) data streams over a single twisted pair. Utilizing advanced 32-level pulse amplitude modulation (PAM); the M28976 operates at speeds up to 4640, or twice the normal G.shdsl rate, enabling operators to double their line utilization at distances of up to 7,000 feet or 2KM. The M28976 offers all of the features provided by the CX28975 multi-mode transceiver including multi-pair operation and guaranteed interoperability with legacy systems including HDSL2, SDSL, and Mindspeed's AutoBaud™ software.

#### **Multimode Operation**

The M28976 DSL solution not only complies with the ITU G.shdsl standard, it also supports the optional enhanced performance asymmetrical PSD (EPAP) modes of operation. In addition, it complies with the ANSI HDSL2 standard (ANSI T1.418) and delivers interoperability with Mindspeed Technologies'™ market-leading ZipWire transceivers through operation in 2B1Q multi-rate mode. The 2B1Q mode supports AutoBaud for SDSL interoperability, rate optimization and fast connect times, as well as standards-based HDSL operation.

### **KEY FEATURES**

- 2 independent full-rate PCM ports for simultaneous operation

- Double the throughput per copper pair of other solutions

- Reliable operation at 4640 Kbps up to 7,000 or 2KM

- Multi-mode operation

- Low-power consumption

- Highly integrated solution

- Embedded microprocessor

- Interoperable with ZipWire 2B1Q transceivers including AutoBaud

All of these modes are supported by a single hardware circuit (i.e., one transformer, crystal and hybrid for all modes) and can be configured in real-time via software control.

#### **Embedded Microprocessor**

The M28976 chipset includes an embedded microprocessor and a full suite of software that facilitates faster and simplified development of systems that comply with all applicable ITU, ANSI and ETSI standards. The embedded microprocessor and software handle the extended operations channel (EOC) processing and many other functions often delegated to an external host controller in competing solutions.

This greatly reduces software-porting efforts and eliminates real-time processing requirements for an external host controller.

#### **Flexible Framer**

The M28976's integrated framer includes fully featured UTOPIA Level 2 and PCM interfaces. The UTOPIA interface includes ATM TC-layer processing. The framer automatically extracts and inserts DSL overhead (i.e., EOC, indicator and Z-bits, CRC, sync word, etc.) and passes it on to the embedded microprocessor. All G.shdsl and HDSL2 frame formats and EOC messaging protocols are supported, as well as other non-standard SDSL frame formats, including framer bypass mode.

#### **Full System Solution**

The M28976 pairs up with an integrated line driver to provide a full DSL solution. The integrated line driver is capable of driving the high line-power EPAP as specified by the G.shdsl standard. The integrated frequency synthesizer, as with the rest of the ZipWirePlus family, supports data rates from 192 Kbps to 4.6 Mbps, and requires only one external crystal. This highly integrated DSL solution enables OEMs to design and manufacture the most feature-rich, lowest-power and highest-density DSL equipment in the industry.

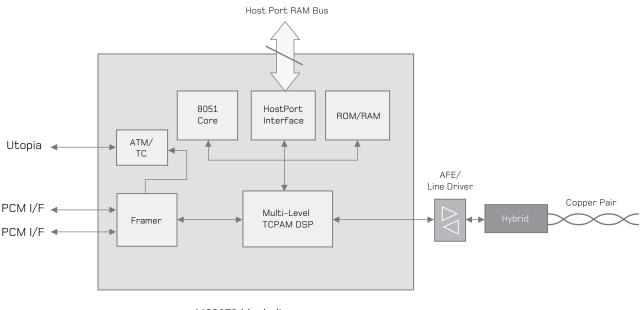

M28976 block diagram

Product Features

- Operating modes supported:

ITU G.shdsl including EPAP modes (ITU G.991.2)

- ITU G.handshake (ITU G.994.1)

- HDSL2 (ANSI T1.418)

- SDSL/2B1Q (AutoBaud)

- HDSL (ITU G.991.1,ETSI 101 135 and ANSI TR-28)

- 4640 operation complies with 2B1Q spectral masks

- Proprietary/extended reach (ANSI spectrum management for loop transmission systems)

- Proprietary/high-speed

(ANSI spectrum management for loop transmission systems)

#### framer, microprocessor, ROM/RAM, frequency synthesizer, DSP, AFE and line driver • Two packaging options for high

Highly integrated solution including

- density and manufacturability

- Option A (two-package):

DSP/Framer/uP = 13x13 mm

- FPBGA; AFE/LD = 7x7 mm LGA

- Option B (two package):

DSP/Framer/uP = 24x24 mm

- LQFP; AFE/LD = 7 x 7 LGA

- Embedded microprocessor for autonomous operation and EOC processing

- Data rates from 192 Kbps to 4.6 Mbps in 8 Kbps increments

- Central office (COT) and remote (RT) operation

- Fast warm startup

- Glueless interface to popular microprocessors

- Single hardware circuit supports all speeds and modes of operation

- +1.8 V, +3.3 V and +12 V power supplies

- JTAG boundary scan

- Operation over full industrial temperature range (-40° C to +85° C)

#### Applications

- DSL-enabled customer premises equipment (CPE)

- Integrated access devices (IADs)

- Digital subscriber line access multiplexers (DSLAMs)

- N-Channel DAML and voice pairgain systems

- Nx64K data transport

- Remote LAN access

- T1 and E1 HDSL-enabled transport systems

- Cellular base station data links

- Campus modems

- Data, voice and video transport systems

www.mindspeed.com/salesoffices

General Information: (949) 579-3000 Headquarters – Newport Beach 4000 MacArthur Blvd., East Tower Newport Beach, CA 92660-3007 Order# 500380A M02-0653 © 2002 Mindspeed Technologies™, a Conexant business. All rights reserved. Mindspeed and the Mindspeed logo are trademarks of Mindspeed Technologies. All other trademarks are the property of their respective owners. Although Mindspeed Technologies strives for accuracy in all its publications, this material may contain errors or omissions and is subject to change without notice. This material is provided as is and without any express or implied warranties, including merchantability, fitness for a particular purpose and non-infringement. Mindspeed Technologies shall not be liable for any special, indirect, incidental or consequential damages as a result of its use.