#### PRELIMINARY

## **XRT86VL32**

REV. P1.0.5

**DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION**

#### JULY 2005

#### GENERAL DESCRIPTION

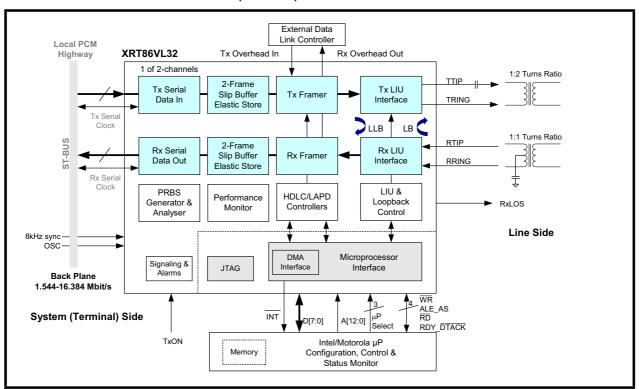

The XRT86VL32 is a two-channel 1.544 Mbit/s or 2.048 Mbit/s DS1/E1/J1 framer and LIU integrated solution featuring  $R^3$  technology (Relayless, Reconfigurable, Redundancy). The physical interface is optimized with internal impedance, and with the patented pad structure, the XRT86VL32 provides protection from power failures and hot swapping.

The XRT86VL32 contains an integrated DS1/E1/J1 framer and LIU which provide DS1/E1/J1 framing and error accumulation in accordance with ANSI/ITU\_T specifications. Each framer has its own framing synchronizer and transmit-receive slip buffers. The slip buffers can be independently enabled or disabled as required and can be configured to frame to the common DS1/E1/J1 signal formats.

Each Framer block contains its own Transmit and Receive T1/E1/J1 Framing function. There are 3 Transmit HDLC controllers per channel which encapsulate contents of the Transmit HDLC buffers into LAPD Message frames. There are 3 Receive HDLC controllers per channel which extract the payload content of Receive LAPD Message frames from the incoming T1/E1/J1 data stream and write the contents into the Receive HDLC buffers. Each framer also contains a Transmit and Overhead Data Input port, which permits Data Link Terminal Equipment direct access to the outbound T1/E1/J1 frames. Likewise, a Receive Overhead output data port permits Data Link Terminal Equipment direct access to the Data Link bits of the inbound T1/E1/J1 frames.

The XRT86VL32 fully meets all of the latest T1/E1/J1 specifications: ANSI T1/E1.107-1988, ANSI T1/E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/E1.408-1990, AT&T TR 62411 (12-90) TR54016, and ITU G-703, G.704, G706 and G.733, AT&T Pub. 43801, and ETS 300 011, 300 233, JT G.703, JT G.704, JT G706, I.431. Extensive test and diagnostic functions include Loop-backs, Boundary scan, Pseudo Random bit sequence (PRBS) test pattern generation, Performance Monitor, Bit Error Rate (BER) meter, forced error insertion, and LAPD unchannelized data payload processing according to ITU-T standard Q.921.

#### APPLICATIONS AND FEATURES (NEXT PAGE)

FIGURE 1. XRT86VL32 2-CHANNEL DS1 (T1/E1/J1) FRAMER/LIU COMBO

REV. P1.0.5

**PRELIMINARY** XRT86VL32 DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION

#### APPLICATIONS

- High-Density T1/E1/J1 interfaces for Multiplexers, Switches, LAN Routers and Digital Modems

- SONET/SDH terminal or Add/Drop multiplexers (ADMs)

- T1/E1/J1 add/drop multiplexers (MUX)

- Channel Service Units (CSUs): T1/E1/J1 and Fractional T1/E1/J1

- Digital Access Cross-connect System (DACs)

- Digital Cross-connect Systems (DCS)

- Frame Relay Switches and Access Devices (FRADS)

- ISDN Primary Rate Interfaces (PRA)

- PBXs and PCM channel bank

- T3 channelized access concentrators and M13 MUX

- Wireless base stations

- ATM equipment with integrated DS1 interfaces

- Multichannel DS1 Test Equipment

- T1/E1/J1 Performance Monitoring

- Voice over packet gateways

- Routers

#### FEATURES

- Two independent, full duplex DS1 Tx and Rx Framer/LIUs

- Two 512-bit (two-frame) elastic store, PCM frame slip buffers (FIFO) on TX and Rx provide up to 8.192 MHz asynchronous back plane connections with jitter and wander attenuation

- Supports input PCM and signaling data at 1.544, 2.048, 4.096 and 8.192 Mbits. Also supports 2-channel multiplexed 12.352/16.384 (HMVIP/H.100) Mbit/s on the back plane bus

- Programmable output clocks for Fractional T1/E1/J1

- Supports Channel Associated Signaling (CAS)

- Supports Common Channel Signalling (CCS)

- Supports ISDN Primary Rate Interface (ISDN PRI) signaling

- Extracts and inserts robbed bit signaling (RBS)

- 3 Integrated HDLC controllers per channel for transmit and receive, each controller having two 96-byte buffers (buffer 0 / buffer 1)

- HDLC Controllers Support SS7

- Timeslot assignable HDLC

- V5.1 or V5.2 Interface

- Automatic Performance Report Generation (PMON Status) can be inserted into the transmit LAPD interface every 1 second or for a single transmission

- Alarm Indication Signal with Customer Installation signature (AIS-CI)

- Remote Alarm Indication with Customer Installation (RAI-CI)

- Gapped Clock interface mode for Transmit and Receive.

- Intel/Motorola and Power PC interfaces for configuration, control and status monitoring

- Parallel search algorithm for fast frame synchronization

- Wide choice of T1 framing structures: SF/D4, ESF, SLC®96, T1DM and N-Frame (non-signaling)

- Direct access to D and E channels for fast transmission of data link information

### **XP EXAR**

REV. P1.0.5

# PRELIMINARY XRT86VL32 DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION

- PRBS, QRSS, and Network Loop Code generation and detection

- Programmable Interrupt output pin

- Supports programmed I/O and DMA modes of Read-Write access

- Each framer block encodes and decodes the T1/E1/J1 Frame serial data

- Detects and forces Red (SAI), Yellow (RAI) and Blue (AIS) Alarms

- Detects OOF, LOF, LOS errors and COFA conditions

- Loopbacks: Local (LLB) and Line remote (LB)

- Facilitates Inverse Multiplexing for ATM

- Performance monitor with one second polling

- Boundary scan (IEEE 1149.1) JTAG test port

- Accepts external 8kHz Sync reference

- 1.8V Inner Core

- 3.3V CMOS operation with 5V tolerant inputs

- 225-pin PBGA package with -40°C to +85°C operation

#### **ORDERING INFORMATION**

| PART NUMBER | Раскаде                     | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------------|-----------------------------|

| XRT86VL32IB | 225 Plastic Ball Grid Array | -40°C to +85°C              |

Your contact: www.codico.com mailto: office@codico.com phone: +43/1/86305-0 fax: +43/1/86305-98